Information, Computing and Intelligent systems.  $-2021. - N_{\odot} 2. - P. 83.$

Recommended for publication by the Academic Council of the Faculty of Computer Science and Computer Engineering

Editor in Chief: Sergii Stirenko

Deputy

editor in Chief: Iryna Klymenko

Responsible

secretary: Liudmyla Mishchenko

Editor board: Sergii Telenyk

Mikolaj Karpinski Nikolai Stoianov Inna Stetsenko Oleksandr Rolik Oleg Chertov Yuri Gordienko Anatoliy Sergiyenko Michail Novotarskiy Yurii Kulakov

Yurii Kulakov Oleksiy Pysarchuk Oleksandr Markovskyi

The scientific journal "Information, Computing and Intelligent systems" is intended for the publication of the results of scientific research and scientific and practical developments in the field of technical sciences by students, masters, PhDstudents, scientists, and practicing specialists in the field of science "Information systems".

The thematic orientation of the journal "Information, computing and intelligent systems" is reflected in the following headings: computerized and computer systems and networks, information technologies, the Internet of Things, information transformation and processing, cloud computing, computer cryptography, data protection, intelligent systems, artificial intelligence, machine learning, automated design of software and technical tools, system control, diagnostics and control of parameters of complex systems, processes and environments; engineering knowledge, embedded systems, robotics, microelectronics.

ISSN 2708-4930

Certificate of state registration No. 23827-13667∏P from 20.02.2019 Magazine in English Web- resource – http://itvisnyk.kpi.ua/ Format 60×84 1/8. Garnitura Times. Offset Folder № 1.

© National Technical University of Ukraine "Igor Sikorsky Kyiv Polytechnic Institute", 2021

# Information, Computing and Intelligent systems

# SCIENTIFIC EDITION

The journal is the legal successor of the Collection of scientific works "Bulletin of NTUU "KPI". Informatics, control and computer engineering"

Founded in 1964 years

**Issue 2**

# **SUMMARY**

| V. Her, V. Taraniuk, V. Tkachenko, I. Klymenko, S. Nikolskyi Methodology of network environment testing for iot devices                                                                 | . 4 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| O. Markovskyi, O. Rusanova, Al-Mrayt Ghassan Abdel Jalil Halil, O. Kot_One approach to accelerate the exponentiation on galois fields for data protection cryptographic systems         | 12  |

| V. Romanuke_Optimal construction of the pattern matrix for probabilistic neural networks in technical diagnostics based on expert estimations                                           | 19  |

| R. Shaptala, G.Kuselov_Vector space models of kyiv city petitions                                                                                                                       | 26  |

| P. Serhiienko, A. Sergiyenko, M. Orlova_Local feature extraction in images                                                                                                              | 35  |

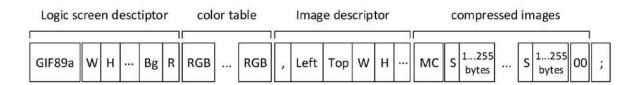

| I. Mozghovyi, A. Sergiyenko, R. Yershov_Gif image hardware compressors4                                                                                                                 | 18  |

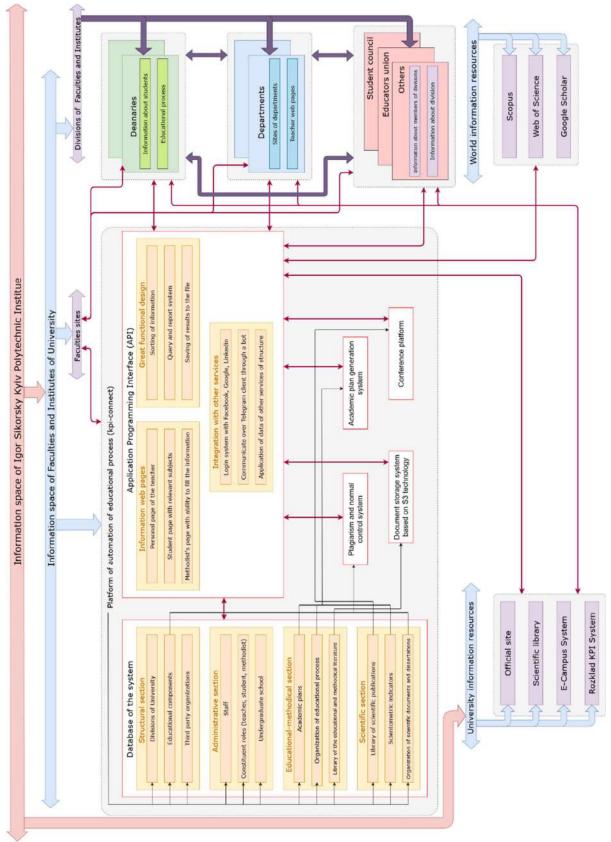

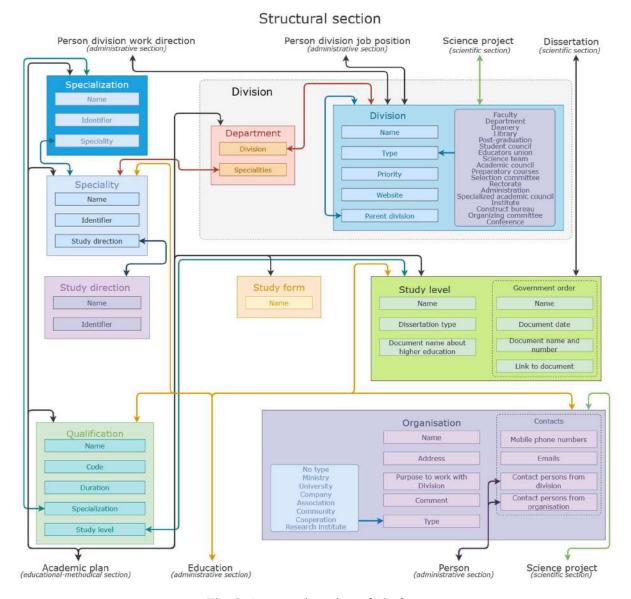

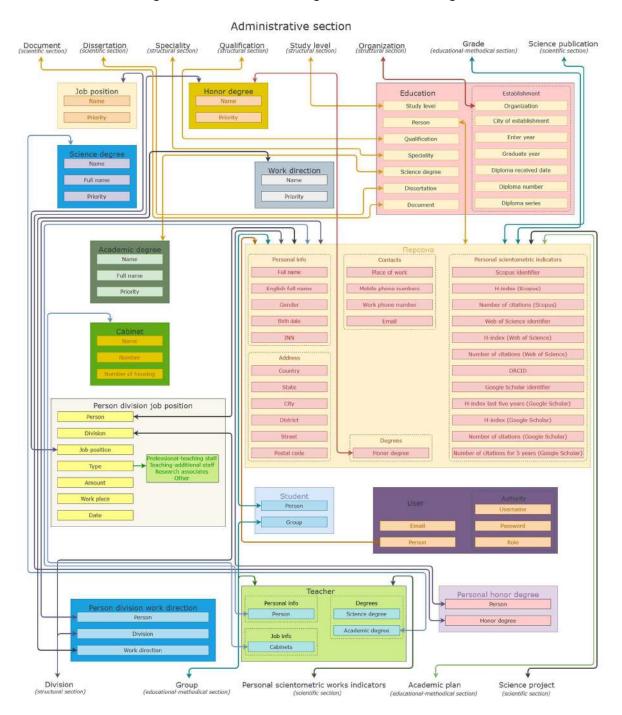

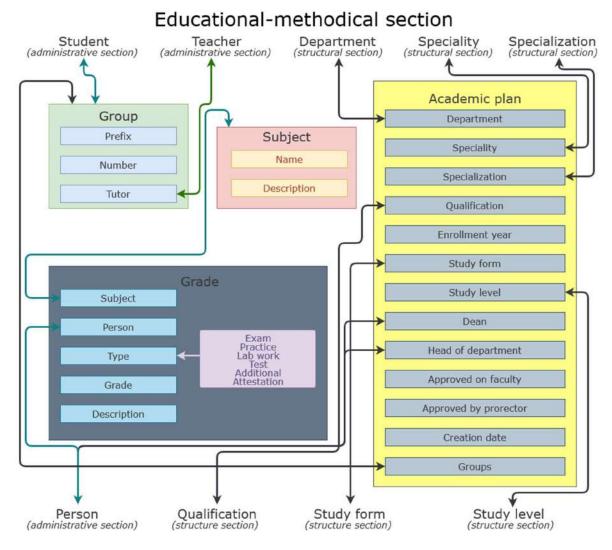

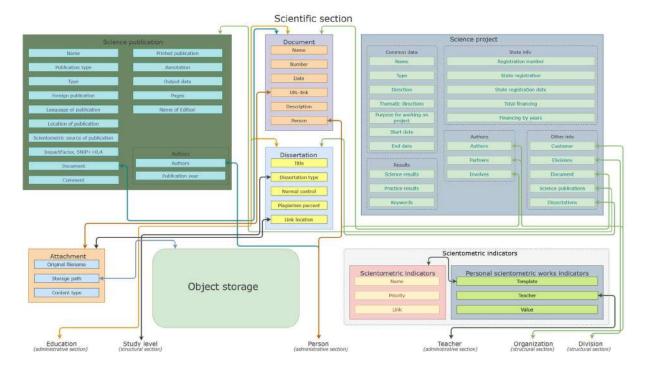

| I. Klymenko, Y. Butskyi, K. Hryshchenko, M. Sivachenko, V. Kryvets, D. Kryvoshei, T. Nguen Architectural review and conceptual development of faculty information system "kpi-connect"5 | 56  |

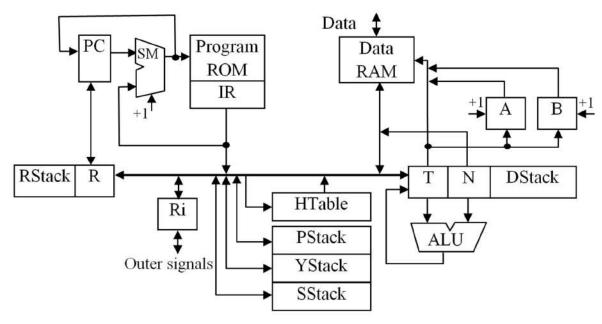

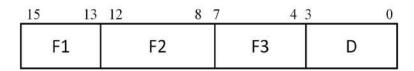

| M. Sergiyenko, O. Molchanov, M. Orlova_Microcontroller for the logic tasks                                                                                                              | 54  |

| Abstracts                                                                                                                                                                               | 73  |

| Анотації                                                                                                                                                                                | 78  |

DOI: https://doi.org/10.20535/2708-4930.2.2021.244169

V. HER V. TARANIUK V. TKACHENKO I. KLYMENKO S. NIKOLSKYI

# METHODOLOGY OF NETWORK ENVIRONMENT TESTING FOR IoT DEVICES

The article reviews methods and technologies for testing the network environment of embedded systems and writing test documentation. As an example, a testing technique based on a defect report has been developed. A performance test was developed to check the load of the embedded device's network environment using special bash scripts for performance testing.

**Keywords:** IoT, embedded system, test case, defect report, troubleshooting, performance testing.

# 1. Introduction

# 1.1 What is the Internet of Things and IoT Testing?

The Internet of Things, or IoT, is a term for billions of devices connected to the Internet. Each of these devices collects data and exchanges it with other devices. The Internet of Things phenomenon is due to the presence of powerful network bandwidth, the proliferation of wireless networks and low-cost computer chips [1-3].

The Internet of Things connects various objects, adds modern sensors and facilitates data exchange between different devices in real time [4]. This allows people to add a new level of digital intelligence to their devices and help them process information locally without any delay.

However, traditional software testing does not work for the Internet of Things [5]. Testers should pay attention to user-centric testing and prevent errors, not detect them. This means that quality assurance engineers have a role to play both in operation and in development.

To guarantee the quality of the software, testers need to gain in-depth knowledge in the subject area. Testers who have no experience testing embedded systems or equipment should develop their skills in these areas.

# 1.2 Importance of IoT Testing

IoT is data exchange and collaboration in real time [3]. Performance issues in any part can negatively affect the performance of another network. One node compromised as a result of a cyber attack can harm others.

Reliable Internet of Things testing ensures system predictability and prevents unexpected failures. You can easily identify weak network nodes in advance and take appropriate measures to increase system reliability. This will provide the end user with a flawless customer experience.

Vulnerabilities in IoT devices will help you determine the reliability of data privacy and digital security. In the absence of reliable cybersecurity, hackers can change the process or falsify data by gaining control of the IoT network. Therefore, before each update, you must thoroughly test the IoT device.

In addition, the fragmented nature of the Internet of Things ecosystem makes testing even more difficult. To do this, you need to have large and reliable test teams equipped with multiple platforms and devices to ensure greater compatibility between different channels [6, 7].

In addition, to ensure that IoT applications work as expected, several other factors need to be considered:

- Ensure that your IoT devices are securely connected to sensors, the cloud, other IoT devices, and other elements needed to ensure unified interaction.

- Make sure the Internet of Things is able to ensure continuity

- Must meet international standards

- Harmonious and flawless work with other interconnected devices of the Internet of Things

- Data obtained from the Internet of Things must be protected from malware and other security vulnerabilities.

Reliable testing of IoT devices is the only effective way to effectively address the above factors. The general approach to quality assurance when testing IoT devices is to reduce testing periods to launch a reliable product with faster market launch. Therefore, it is important to conduct testing from the beginning of the development phase to identify and correct deficiencies at an early stage.

**Problem statement:** It is necessary to test IoT devices in order to avoid improper operation, which can lead to fatal consequences (such as security problems, communication problems, failure of sensors or the device itself, etc.). To prevent such problems, it is necessary to thoroughly test the IoT devices and their network environment before use.

# 2. Review of existing solutions and their use

Embedded systems are used in a wide range of technologies in various industries [2, 3]. Some examples:

Cars. Modern machines usually consist of many computers (sometimes up to 100) or embedded systems designed to perform various tasks in the vehicle. Some of these systems perform basic utility functions, while others provide entertaining or user-oriented functions. Some embedded systems in consumer cars include cruise control, backup sensors, suspension control, navigation systems and airbag systems.

**Mobile Phones**. They consist of many embedded systems, including graphical user interface software and hardware, operating systems (OS), cameras, microphones, and USB I / O modules (universal serial bus).

**Industrial machines**. They may contain embedded systems, such as sensors, and may themselves be embedded systems. Industrial machines often have built-in automation systems that perform specific control and management functions.

**Medical equipment**. They may include embedded systems such as sensors and controls. Medical equipment, like industrial machines, must also be very user-friendly so that machine errors that can be prevented do not endanger human health. This means that they will often include more complex operating systems and a graphical interface designed for the corresponding interface.

There are many examples of embedded systems. So, the article will show several examples and analyze their use, as well as their structure.

# **Automotive Embedded Systems:**

Electronic control units are used in automotive embedded systems. This unit contains a microcontroller, switches, sensors, drivers, etc. All sensors and actuators are connected to the electronic control unit. Cars that use embedded systems can consist of hundreds of microprocessors. Each microcontroller performs its own special task. Some of them control the engine. Some launch the dashboard device. The whole system actually consists of several small systems. The use of embedded systems in the automotive industry has reduced the cost factor. This has improved overall performance and increased functionality. It has also reduced weight and made cars safer and more reliable. Applications of automotive embedded systems include [5]:

- Automatic stability control

- Traction control system

- Pre-emergency safety system

- Airbag

- Car navigation system

So you can see that embedded systems have improved cars and made them more comfortable. Also, they have increased the functionality of cars and made them easy to use.

# **Home Security System:**

Home security systems are widely used today [1]. These systems have several functions, such as checking for fire or gas leaks, as well as detecting attempts by a suspicious person to enter the

house. The microcontroller is used to control all operations. Sensors give data and if something wrong happens then safety alarms get activated. Sensors used in such systems include gas sensors, smoke sensors, temperature sensors, IR sensors, etc. Such systems also include a keyboard for entering passwords on the gate. If the correct password is entered, this built-in system opens the gate, and if someone tries to enter the wrong password, the alarm goes off and the gate remains closed. The output signal comes from alarms or any display. The conclusion can also be sent to a remote location. If family members are not at home, they can still monitor what is happening in their home. The home security system is not limited to homes. Such systems can be used in stores, shops and in production. Almost every industry and office has security systems that can recognize workers by their faces or IDs. The home automation system is also one example of embedded systems as a home security system.

# 3. What is an embedded system?

# 3.1 Embedded systems

An embedded system is a computer system with a specific function in a larger mechanical or electrical system. They control many commonly used devices. They consume little energy, are small in size and their cost is low per unit. Modern embedded systems are often based on microcontrollers. A microcontroller is a small computer on a single integrated circuit that contains a processor core, memory, and programmable I/O peripherals. Because the embedded system is designed to perform certain tasks, they can be optimized to reduce the size and cost of the product, as well as increase reliability and performance [6].

Embedded systems have revolutionized science. It is also part of the Internet of Things (IoT), a technology in which objects, animals, or people are given unique identifiers and the ability to transmit data over a network without requiring human-to-human or human-to-computer interaction.

# 3.2 How embedded systems work

Embedded". These are inexpensive, low-power, small computers built into other mechanical or electrical systems. They typically consist of a processor, power supply, memory, and communication ports. Embedded systems use communication ports to transfer data between the processor and peripherals - often other embedded systems - using a communication protocol. The processor interprets this data using minimal software stored in memory. Software is usually highly dependent on the function performed by the embedded system. The processor can be a microprocessor or a microcontroller. Microcontrollers are just microprocessors with peripheral interfaces and built-in memory. Microprocessors use separate integrated circuits for memory and peripherals instead of including them in the chip. Both can be used, but microprocessors usually require more support circuits than microcontrollers because they are less integrated into the microprocessor.

# 3.3 The structure of embedded systems

Embedded systems vary in complexity, but usually consist of three main elements:

- Hardware. The hardware of embedded systems is based on microprocessors and microcontrollers. Microprocessors are very similar to microcontrollers and usually refer to a CPU (CPU) that is integrated with other basic computing components, such as memory chips and digital signal processors (DSP). These components are built into the microcontrollers on a single chip.

- Software and firmware. Embedded software software can vary in complexity. However, industrial-grade microcontrollers and embedded IoT systems typically run very simple software that requires a small amount of memory.

- Real time operating system. They do not always work in embedded systems, especially in smaller systems. RTOS determine how the system works by controlling the software and setting rules during program execution.

In terms of hardware, a basic embedded system would consist of the following elements:

Sensors convert physical sense data into an electrical signal.

- Analog-to-digital (A-D) converters change an analog electrical signal into a digital one.

- Processors process digital signals and store them in memory.

- Digital-to-analog (D-A) converters change the digital data from the processor into analog data.

- Actuators compare actual output to memory-stored output and choose the correct one.

The sensor reads external inputs, the converters make that input readable to the processor, and the processor turns that information into useful output for the embedded system.

# 3.4 Types of embedded systems

There are several basic types of embedded systems that differ in their functional requirements. Among them are:

- Mobile embedded systems are small systems designed for easy use and everyday portability.

An example of this is digital cameras.

- Network-embedded systems are connected to the network to provide output to other systems.

Examples are home security and point of sale (POS) systems.

- Standalone embedded systems do not depend on the main system. Like any embedded system, they perform a specialized task. However, they do not necessarily belong to the host system, unlike other embedded systems. An example of this is a calculator or MP3 player.

- Embedded systems in real time give the desired result after a certain time interval. They are often used in the medical, industrial and military sectors because they are responsible for the most important tasks that depend on time. An example of this is the traffic control system.

Embedded systems can also be categorized by their performance requirements:

- Small-scale embedded systems often use no more than an 8-bit microcontroller.

- *Medium-scale embedded systems* use a larger microcontroller (16-32 bit) and often link microcontrollers together.

- Sophisticated-scale embedded systems often use several algorithms that result in software and hardware complexities and may require more complex software, a configurable processor and / or a programmable logic array.

There are several common architectures of embedded system programs that become necessary as embedded systems grow and become more complex in scale. They include:

- Simple control cycles caused by routines that control a specific piece of equipment or firmware.

- Interrupt control systems have two cycles: primary and secondary. Interrupts in cycles cause tasks

- *Cooperative multitasking* is essentially a simple control loop located in the Application Programming Interface (API).

- *Warning multitasking or multithreading* is often used with real-time operating systems (RTOS) and has strategies for synchronizing and switching tasks.

To sum up: Today, any embedded system is an IoT device that connects to the Internet and can communicate with other IoT devices. Also, the proposed complex allows you to test the network environment of the embedded system.

# 4. Types of test documentation and methodology

#### 4.1 Test documentation

The basis of testing is knowledge and ability to write test documentation, as well as knowledge of different testing methodologies. There are three main types of documentation: test case, defect report, and troubleshooting. There are also different approaches and testing methods. Examples based on the TCP protocol stack will be shown. Let's take a closer look at the test documentation, which is aimed at helping developers and testers improve the product being developed.

Test case: A test case is a set of actions performed on a system to determine whether it meets the requirements of the software and is functioning properly [8]. The purpose of the test case is to

determine whether the various functions in the system work as expected and to confirm that the system meets all relevant standards, guidelines and customer requirements. The process of writing a test case can also help detect errors or defects in the system. Test cases are typically written by members of the quality assurance team (QA) or testing team, and can be used as step-by-step instructions for each system test.

**Defect report**: This is a document that identifies and describes a defect detected by a tester or user [9]. The purpose of the defect report is to state the problem as clearly as possible so that the developers can easily reproduce the defect and correct it. Writing software bug reports is an important skill for software testers, quality control. The defect report contains a sequence of actions that leads to an unexpected result, or the user receives an unexpected error: the system hangs, or the calculated data is inaccurate, and so on.

**Troubleshooting:** Troubleshooting is the process of diagnosing the source of a problem. It is used to troubleshoot hardware, software, and many other products. The basic theory of troubleshooting is that you start with the most general (and often the most obvious) possible problems and then narrow them down to more specific issues [10].

Few testing methodologies:

**Performance testing** - testing, which is carried out in order to determine how quickly a computing system or part of it works under a certain load. It can also be used to check and validate other attributes of system quality such as scalability, reliability, and resource consumption. This method will be described in more detail in Section 6, using the TCP protocol stack as an example.

**Security testing**: Application security for IoT devices is probably the biggest problem for most users. People can use applications for IoT devices for a variety of reasons, including monitory transactions, sharing personal information, buying and selling, and more. That's why the Internet of Things app needs to have special access control tools for users that restrict access to outsiders. Without security testing, it is impossible to detect major vulnerabilities in the application of the Internet of Things device and make sure that it does not transmit confidential information to attackers.

**Required hardware and software:** To test the TCP protocol stack, you need to have two computers with Linux installed, as well as a number of programs: wireshark (analog of the tcpdump traffic interceptor with a convenient and clear interface, iperf – TCP / UDP traffic generator, which allows you to check system stability, dhcp – server, and also some built-in Linux utilities).

# 4.2 Example of test documentation

Shown as an example one of the most popular types of test documentation, namely a defect report. A defect report is needed so that developers can quickly fix errors. Defect reports should include detailed information about the platform, environment, or other technical information to create detailed description. Your defect report should be clear and easy to read. The purpose of the defect report is to resolve the issue as soon as possible so that customers can continue to use the software. Here are the main sub-items for the report:

- Summary

- Description

- Build / platform

- Playback steps

- Actual results

- Expected results

This way, the developer or manager can quickly get a clear idea of the error. The developer will be able to quickly reproduce the error using step-by-step instructions, and then correct it.

Here is an example of a report defect that describes a failed dhcp server startup and suggests a solution to this problem.

**Summary:** DHCP doesn't start **OS:** Ubuntu 20.04 Severity: Minor

**Priority:** Medium Status: Assigned

**Description:** DHCP doesn't start because dhcpd.conf isn't configured correctly

# **Steps to Reproduce:**

Configure: dhcpd.conf

Start dhcp: sudo dhcpd

3.Check DHCP status sudo systemctl status isc-dhcp-server

```

Escapho-server. service . ISC Dich IPv4 server

Loaded: Loaded (7 lbs/system/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fystem/fy

```

Fig. 1. Example of a failed DHCP server startup

Actual result: DHCP server failed to start due to incorrect dhcpd.conf configuration

**Expected result:** DHCP server started successfully

Fig. 2. An example of a successful start of a DHCP server

**HowTo Fix:** Configure *dhcpd.conf* right. In this case, write the subnet mask correctly

# 5. Results. Performance test

Performance testing is the practice of assessing how a system works in terms of response speed and stability under a given workload. Performance tests are usually performed to check the speed, stability, reliability and size of the program. The process includes such indicators of "effectiveness" as:

- Browser, page and network response time

- Server request processing time

- Simultaneous custom volumes are allowed

- CPU memory consumption; the number and type of errors that may occur in the application

In our case, testing the stability of the system will be demonstrated using bash scripts that are

very easy to write and use. An example of such a scenario is shown below.:

```

#!/bin/bash

print_usage() {

echo "Usage: $0 ip_addr device"

}

if [ $# -ne 2 ]; then

echo "Error: Too few arguments" >&2

print_usage

exit 1

fi

iperf -c $1 -i 1 -t 30 | tee tcp_$2.txt

```

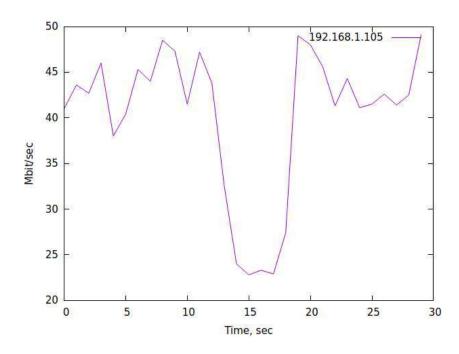

This script uses an *iperf* traffic generator that requires a client and a server. This script accepts the IP address of the server and the client. You can also select the desired script execution time and the interval at which the result will be displayed. At the output we get a text file with a traffic log.

Next, you can use the *gnuplot* script, which can be used to draw a graph that will use \*.txt traffic derived from the *bash* script. Further is an example of a *gnuplot* script:

```

set xlabel "Time, sec"

set ylabel "Mbit/sec"

files = system("ls -1 *.txt")

phone(f) = substr(f, 5, strlen(f) - 4)

plot

for [file in files] file

using ($3>8 ? $7 : $8) \

every ::6

title phone(file)

with lines

pause mouse close

```

You must make both scripts executable. To do this, use the command:

sudo chmod + x <file name>.

You can now run these scripts sequentially and get the result as a graph (fig. 1).

Fig. 3. Generated traffic graph

# 6. Conclusion

Today, the Internet of Things is one of the most popular industries. Therefore, in the development of IoT devices there is a need for detailed testing of these devices. If you do not fully test the device before selling it, many malfunctions may occur in the future, and this will result in the loss of a large amount of money for the company. Also this article discusses the basics of testing: writing test documentation, and some testing methods. The writing of the defect report on an example of start of the dhcp server was considered in more detail, and also the performance test which uses the usual bash script as a basis was demonstrated.

# References

- [1] "Real Life Examples of Embedded Systems," *The Engineering Projects*, Nov. 12, 2016. https://www.theengineeringprojects.com/2016/11/examples-of-embedded-systems.html

- [2] "What is embedded system?" *IoT Agenda*, 2019. https://internetofthingsagenda.techtarget.com/definition/embedded-system

- [3] "How Embedded Systems Impact Your Everyday Life," *Electronics Maker*, Apr. 13, 2018. https://electronicsmaker.com/how-embedded-systems-impact-your-everyday-life

- [4] W. Wolf, B. Ozer, and T. Lv, "Smart cameras as embedded systems," *Computer*, vol. 35, no. 9, pp. 48–53, Sep. 2002, doi: https://doi.org/10.1109/mc.2002.1033027.

- [5] TechSci Research, https://www.techsciresearch.com, "Embedded Systems- The Heart of Automotive Market," *Techsciresearch.com*, 2017. https://www.techsciresearch.com/blog/embedded-systems-the-heart-of-automotive-market/44.html

- [6] "Importance of IoT Testing, what is Internet of Things testing types and process," *PFLB*, Jun. 05, 2020. https://pflb.us/blog/iot-testing-importance/

- [7] R. L. Mitchell, "The Internet of Things at home: Why we should pay attention," *Computerworld*, Jun. 30, 2014. https://www.computerworld.com/article/2696046/the-internet-of-things-at-home-why-we-should-pay-attention.html

- [8] T. Hamilton, "How to Write Test Cases: Sample Template with Examples," *Guru99.com*, Mar. 23, 2019. https://www.guru99.com/test-case.html

- [9] A. Reichert, "How to write a software defect report," *TechBeacon*. https://techbeacon.com/app-dev-testing/write-software-defect-reports-get-results-boost-credibility

- [10] "Computer Basics: Basic Troubleshooting Techniques," *GCFGlobal.org*, 2019. https://edu.gcfglobal.org/en/computerbasics/basic-troubleshooting-techniques/1/

O. MARKOVSKYI, O. RUSANOVA AL-MRAYT GHASSAN ABDEL JALIL HALIL O. KOT

# ONE APPROACH TO ACCELERATE THE EXPONENTIATION ON GALOIS FIELDS FOR DATA PROTECTION CRYPTOGRAPHIC SYSTEMS

The new approach to accelerate the computational implementation of the basic for a wide range of cryptographic data protection mechanisms operation of exponentiation on Galois Fields have been proposed. The approach is based on the use of a specific property of a polynomial square and the Montgomery reduction. A new method of squaring reduces the amount of computation by 25% compared to the known ones. Based on the developed method, the exponentiation on Galois Fields procedure has been modified, which allows to reduce the amount of calculations by 20%.

**Keywords:** multiplication operation on Galois fields, cryptographic algorithms based on Galois Fields algebra, Galois Fields exponentiation, Montgomery reduction.

# 1. Introduction

The dynamic development of the Internet and computer technology has led to the emergence and widespread use of cloud technologies. These technologies provide a wide range of users with access to virtually unlimited computing power, large amounts of memory and modern software. Thus, cloud technologies can significantly increase the capabilities of the widest range of users to solve their scientific and applied problems.

On the other hand, access to these technologies has become more accessible not only to ordinary users, but also to villains, who were among the first to join the opportunities offered by cloud technology [1]. The tasks of selecting keys to existing cryptographic mechanisms for information security are well parallelized and, accordingly, effectively solved on powerful multiprocessor remote computer systems [2]. Thus, the advent of cloud technology has objectively upset the balance between the level of cryptocurrency and the resources available to villains [2]. To counteract this, there is a need to find new ways to increase the level of cryptocurrency, first of all, public key information protection algorithms. Most of these algorithms are based on the mathematical operation of modular exposition, which is performed on large numbers (2048 or 4096).

One possible solution to this problem is to increase the bit size of the keys used in the corresponding cryptographic algorithms. However, such a decision will result in a significant slowdown in the computational implementation of cryptographic protection mechanisms. In particular, doubling the bit size slows down the execution of algorithms eight times [3].

Another solution to the problem of accelerating the computational implementation of cryptographic algorithms with a public key is to move to another algebraic basis, in particular to the algebra of Galois fields [4]. Operations in these fields are performed an order of magnitude faster due to the lack of hyphens. Further acceleration can be achieved through the use of additional resources. To use them, it is necessary to develop new methods aimed at accelerating the execution of the exposure operation in the Galois fields.

Thus, the scientific task of accelerating the execution of the exposure operation in the Galois fields is relevant at the present stage of development of information technology.

# 2. Problem statement and review of methods for its solution

The tendency to expand the use of exposure to Galois fields in modern mechanisms of cryptographic protection of information stimulates intensive research aimed at accelerating the performance of multiplicative operations on numbers whose bit size far exceeds the bit size of the processor [5].

In the transition in cryptographic using to the algebra of Galois fields from traditional algebra, in order to distinguish operations in each of these algebras use different notation. In particular, in the algebra of Galois fields, the traditional addition is replaced by the addition operation in the Galois fields, which is denoted by the symbol ' $\oplus$ ' is a bitwise operation "Excluding OR" (XOR). In the algebra of Galois fields there is no subtraction operation usual in traditional algebra. The basic multiplication operation in the Galois field algebra consists of two operations: polynomial multiplication and reduction using a base polynom of the field [6]. The polynomial multiplication is denoted by the symbol ' $\otimes$ ', and the reduction operation consists in calculating the remainder of the polynomial division of the result of the polynomial multiplication by the Galois field forming the polynomial P(x) [6]. The operation of calculating the remainder of the polynomial division of the number A by P is denoted as A rem P. The product of the numbers A and B in the Galois fields is denoted as  $A \otimes B$  rem P. The operation of calculating exponents on Galois fields, is the calculation of the polynomial remainder from the division of the product E of the numbers A by the polynomial field P is denoted as A rem P in contrast to the modular exposition A mod M adopted in traditional algebra [6].

The existing methods of exposition on Galois fields are based on two classical algorithms: from the lower and upper bits of the code the exponents  $E = \{e_n, e_{n-1}, ..., e_0\}$  for any  $j \in \{1, 2, ..., n-1\}$ ;  $e_i \in \{0, 1\}$ . In both mentioned algorithms it is impossible to perform several cycles simultaneously [7]. The advantage of the lower-bit exponential algorithm is the ability to partially parallelize calculations within a single cycle. This allows you to increase the speed of the algorithm by 1.5 times.

Further acceleration of the exponent operation in Galois fields is carried out by reducing the execution time of multiplication in the field [8]. This operation consists of polynomial multiplication and reduction. The operation of polynomial multiplication of n-bit numbers requires 0.5n logical addition operations and n shift operations to calculate the product. Taking into account that the execution time of the logical addition command is approximately the same as the execution time of the shift command, we can assume that the implementation of polynomial multiplication is determined by the execution time of 1.5n logical operations [9]. As the main reserve for accelerating multiplication in Galois fields, most researchers consider the reduction operation [10].

The polynomial reduction operation is performed by adding a number corresponding to the forming polynomial to the current remainder. This operation includes determining the position of the highest digit of the current remainder, shifting the code forming the polynomial, logically adding it to the current remainder [11]. Thus, to perform the reduction, you need to perform an average of n bit testing operations, 2n offset operations (offset code of the forming polynomial and test code containing one unit), as well as 0.5n logical addition operations. The total average number of logical operations to perform reduction by dividing polynomials is 3.5n.

Further increase in speed is achieved by accelerating the reduction. Most of the known methods are based on the use of precalculations dependent on the unchanging polynomial P [12], which in cryptographic information protection systems is part of the public key and, accordingly, rarely changes.

In acceleration methods based on the use of this property of the forming polynomial, the residues from the division of the codes  $2^{n+1},...,2^{2\cdot n}$  by the forming polynomial P(x):  $T_1 = 2^{n+1}$  rem P,  $T_2 = 2^{n+2}$  rem  $P,...,T_n = 2^{2\cdot n}$  rem P are preliminarily calculated. The calculated codes are stored in the table memory of precalculations. The reduction is reduced to the addition of tabular codes, which correspond to the units in the highest n digits of the code of the polynomial product. Thus, due to the use of precalculations, it is possible to reduce the average number of logical operations to implement the reduction to 1.5n. The total average number of logical operations for multiplication on Galois fields is 3n.

Another way to accelerate the reduction in Galois fields is proposed in [13, 14] and its essence is to adapt the Montgomery technology known in traditional algebra to the features of the algebra of

Galois fields. Using Montgomery technology, the average number of logical operations for the computational implementation of multiplication in Galois fields was reduced to 2n rounds [15].

An analysis of both classical Galois finite-field exposition algorithms shows that 2/3 of the computational volume is accounted for by the square operation. Therefore, the most promising way to accelerate these important cryptographic calculations is to conduct research aimed at reducing the computational complexity of squaring in the Galois fields.

# 3. Purpose and objectives of research

The aim of the study is to accelerate the calculation of the exponent on the finite Galois fields in software and hardware implementation by reducing the number of logical operations required for squaring in the Galois fields.

To achieve this goal, the study solves the following tasks:

- analysis of the features of symmetry of operations when squaring in Galois fields and finding ways to use them to accelerate squaring the basic operation of exposition in Galois fields;

- development of a method of accelerated squaring in the Galois fields, the difference of which is to eliminate duplication of calculations, thereby reducing the computational complexity;

- development of a modified exposition procedure in Galois fields using the accelerated method of squaring;

- evaluation of the effectiveness of the proposed method of squaring in the Galois fields and exposition in terms of accelerating their computational implementation.

# 4. The method of accelerated elevation to the square in the Galois fields using the Montgomery reduction

Twothirds of the computational volume that makes up the Galois field exponentiation, as well as the traditional modular exposition, is the squaring operation [8]. Therefore, it is important to find opportunities to accelerate this dominant component of the implementation of cryptographic mechanisms in the transition from traditional modular exposure to perform this operation in Galois fields.

The property of a polynomial square and the application of the Montgomery reduction can be considered as the main reserves for the acceleration of calculations related to the squaring in the Galois fields.

The property of a polynomial square is that the addition to the square of the number  $A = a_{n-1} \cdot 2^{n-1} + a_{n-2} \cdot 2^{n-2} + ... + a_1 \cdot 2 + a_0$ , where  $\forall i \in \{0,1,...,n-1\}: a_i \in \{0,1\}$  is reduced to the insertion of "zeros" between the binary digits  $a_0$ ,  $a_1$ ,..., $a_{n-1}$  of the number A:  $A \otimes A = A^2 = a_{n-1} \cdot 2^{2 \cdot (n-1)} + a_{n-2} \cdot 2^{2 \cdot (n-2)} + ... + a_1 \cdot 4 + a_0$  [11]. For example, if  $A = 9_{10} = 1001_2$ , then its polynomial representation has the form:  $A(x) = x^3 + 1$ . Accordingly, the polynomial square of this number can be represented as:  $A(x) \otimes A(x) = (x^3 + 1) \cdot (x^3 + 1) = x^6 + x^3 + x^3 + 1 = x^6 + 1$ . Inserting "zeros" between binary digits gives a similar result:  $A^2 = 1 \cdot 0 \cdot 0 \cdot 0 \cdot 0 \cdot 1_2 = 65$ .

Thus, the first component of squaring in the Galois fields – polynomial multiplication does not require for its implementation any operations other than shifts. Montgomery technology adapted to Galois field algebra can be used to accelerate the computational implementation of the second component, the reduction of a polynomial square [12].

To realize the above possibilities, the following method of squaring in Galois fields is proposed. There is a number A such that  $A = a_{n-1} \cdot 2^{n-1} + a_{n-2} \cdot 2^{n-2} + ... + a_1 \cdot 2 + a_0$ , and  $\forall i \in \{0,1, ..., n-1\}: a_i \in \{0,1\}$ . It is necessary to perform the operation of squaring this number to the square, ie to calculate  $A \otimes A^2$  rem P, where P is the number that corresponds to the forming polynomial of the Galois field:  $P = p_n \cdot 2^n + p_{n-1} \cdot 2^{n-1} + p_{n-2} \cdot 2^{n-2} + ... + p_1 \cdot 2 + p_0$ ;  $\forall j \in \{0,1,...,n\}: p_j \in \{0,1\}$ . Montgomery's technology involves the use of an auxiliary polynomial R,  $R = 2^n$  for which the multiplicative inversion  $R^{-1}$  is determined so that  $R \cdot R^{-1}$  rem P = 1.

The proposed method involves the following sequence of actions:

1. The counter j cycles is set to zero: j = 0.

- 15 Information, Computing and Intelligent systems  $N \ge 2$ 2. The number B is formed:  $B: B = b_{2n-1} \cdot 2^{2n-1} + b_{2n-2} \cdot 2^{2n-2} + ... + b_1 \cdot 2 + b_0$  and  $\forall k \in \{0,1, ..., 2n-1\}$ :  $b_k = a_{k/2}$ , if  $k \mod 2 = 0$  and  $b_k = 0$  if  $k \mod 2 = 1$ .

- 3. If  $b_0 = 0$ , then proceed to claim 5.

- 4. To the current value of the code B is added modulo 2 the value of the code P, which corresponds to the forming polynomial of the code:  $B = B \bigoplus P$ .

- 5. A shift to the right by one bit of the value of the code B of the current result:  $B \gg 1$ ;

- 6. The unit is added to the cycle counter: j = j + 1. If j < n, then there is a return to re-execution of claim 3.

Next will be show that as a result of the proposed procedure it obtained the value of the result B, which is equal to  $A \otimes A \otimes R^{-1}$  rem P. If we denote by D the polynomial square  $D = A \otimes A$ , which is obtained by inserting "zeros" between each pair of binary digits of the number A, the value of D is equal to the initial value of B, which is formed in paragraph 2 of the developed procedure. In the process of its implementation to the value of D are added h values of the number P, where  $0 \le h \le n$ . The addition of the numbers P is carried out in such a way that their logical sum with the code D has zeros in n lower digits. That is, the code B', which is obtained as a result of the above procedure, excluding offsets, can be represented as:  $B' = A \otimes A \oplus S$ , where S is the logical sum h of shifted codes P. Offset of the obtained result B' by n positions to the right, provided that the lower n bits of B' are equal to zero, equivalent to the multiplication of B' by the multiplicative inversion R-1 of the code R =2n, the multiplication by which is identical to the shift operation to the left by n bits. Thus, the code B obtained as a result of the procedure described above is a reduction of the product:  $B' \otimes R^{-1} = (A \otimes A \oplus S) \otimes R^{-1} = (A \otimes A) \otimes R^{-1} \oplus S \otimes R^{-1}$ . In other words,  $B = B' \otimes R^{-1}$  rem  $P = (A \otimes A) \otimes R^{-1}$  rem  $P \oplus S \otimes R^{-1}$  rem P. Due to the fact that the second component of the sum includes as a component of the product the sum of codes P, then the value of its remainder from the polynomial division by P is zero. This means that the obtained, as a result of the proposed and described above procedure is equal to  $B = (A \otimes A) \otimes R^{-1}$  rem P, which had to be proved.

The proposed algorithm can be illustrated by the following numerical example.

Let n = 4,  $A = 11_{10} = 1011_2$ , forming polynomial  $P = 19_{10} = 10011_2$ , an auxiliary polynomial R = 2n = 16, and its multiplicative inversion is equal to  $R^{-1} = 14_{10} = 1110_2$ . Indeed,  $R \cdot R - 1$  rem P = 16.14 rem 19 = 1. It is necessary to raise to the square of the number A on the Galois field with the forming polynomial P(x) = x4 + x + 1, which is related to the number P = 19:  $A \otimes A$  rem  $P = 11 \otimes 11 \text{ rem } 19 = 9.$

Before performing the calculations, according to claim 1 of the above procedure, the counter i cycles is set to zero, and the initial value of the number B is formed from a given number A by inserting zeros: B = 1000101.

The dynamics of transformations of variable B in the process of performing cycles of the above procedure is presented in table 1.

Dynamics of transformations of variable B in the process of performing cycles of the proposed procedure of accelerated squaring in the Galois fields

|   | The value of the variable B   |       |                         |                         |  |  |  |  |  |

|---|-------------------------------|-------|-------------------------|-------------------------|--|--|--|--|--|

| j | At the beginning of the cycle | $b_0$ | After performing step 4 | After performing step 5 |  |  |  |  |  |

|   |                               |       | 1000101                 |                         |  |  |  |  |  |

| 0 | 1000101                       | 1     | ⊕ <u>10011</u>          | 101011                  |  |  |  |  |  |

|   |                               |       | 1010110                 |                         |  |  |  |  |  |

|   |                               |       | 101011                  |                         |  |  |  |  |  |

| 1 | 101011                        | 1     | ⊕ <u>10011</u>          | 11100                   |  |  |  |  |  |

|   |                               |       | 111000                  |                         |  |  |  |  |  |

| 2 | 11100                         | 0     | _                       | 1110                    |  |  |  |  |  |

| 3 | 1110                          | 0     | _                       | 111                     |  |  |  |  |  |

The number *B* obtained as a result of the proposed procedure of accelerated ascent to the square is equal to  $A \otimes A \otimes R^{-1}$  rem  $P = 11 \otimes 11 \otimes 14$  rem 19 = 7.

The true value of U of the square A on the Galois field with the forming polynomial  $P(x)=x^4+x+1$ , which corresponds to the number P=19 can be obtained by multiplying B by  $R=2^n=2^4=16$ :  $U=7\otimes 16$  rem 19=9.

According to conducted research, the average multiplication time in Galois fields depends on the number of logical addition and shift operations.

In a known variant of multiplication in the fields of the Montgomery Reduction [14], the shift is performed on each of n cycles, so is performed n times. Operations of logical adding the multiplicand to current result are carried out when the current bit of the multiplier is equal to one. On large length, the probability that the current bit will be a one or zero, is equal to 50%, thus, the multiplicand logical addition will occur only in half of all cycles, that is  $0.5 \cdot n$  times. Operations of logical adding of Galois fields base polynomial depends on low bit of current result. Thus, in average this operation is executed also  $0.5 \cdot n$  times [16]. Then, the average total number of logical addition operators consist of n. Logical addition and shift operations require approximately the same time to execute. Therefore, it is advisable to calculate all operations together when calculating the time of the algorithm together. And the total number of all operations will be  $2 \cdot n$ .

In the developed method, the rise time to the square depends on number of shifts and number of logical addition operations. Adding a multiplicand in proposed method was replaced by the previous and disposable insertion of zeros. Shifts occur on each cycle, that is their number n. As in a well–known method, the logical addition operation number depends on the low bit of current result. Therefore, the average numbers of such operations is equal to 0.5n. Acceleration occurs due to the exclusion of logical adding of multiplicand. Thus, in the algorithm according to the proposed method, the average total number of operations for square on Galois field calculation is 1.5n.

Compared to the time of execution of a previously existing multiplication algorithm by Montgomery method [15], the number of operations decreased from  $2 \cdot n$  to  $1.5 \cdot n$ , that is, by 25%. The conducted experimental studies were obtained by the theoretical evaluation.

# Organization of the calculation of the exponent in the Galois field using the proposed method of squaring

As noted above, squaring in the Galois field is about 2/3 of the process of calculating the exponent in the Galois field – the basic operation of a wide class of cryptographic algorithms.

Accordingly, the squaring by the proposed method, which combines the use of a polynomial square and the Montgomery reduction, can be effectively used to accelerate the exposure in the Galois fields. The squaring operation performed by the proposed and described method is hereinafter referred to as KM (Montgomery Square) in contrast to the known multiplication scheme in Galois fields using Montgomery recursion [13] which is denoted as MM.

Modified in this way the exposition procedure on Galois fields, the calculation of  $A^E$  rem P involves performing precalculations before the start of cycles of sequential processing of bits of the exponent code. Montgomery technology determines the use of the auxiliary polynomial R(x) and its multiplicative inversion  $R^{-1}(x)$ . The number R corresponding to the polynomial  $R(x) = x^n$  is defined as  $R = 2^n$ ; accordingly, the multiplicative inversion  $R^{-1}(x)$  is correlated with the number  $R^{-1}$  such that  $R \otimes R^{-1}$  rem P = 1. In addition, the reduction technology according to the Montgomery method involves performing precalculations before exponentiation, namely: calculation G = R rem  $P = R \oplus P$  and

$D = R|^2$  rem P, as well as  $Z = MM(A, D) = A \otimes D \otimes R^{-1}$  rem P. It is obvious that the values of G, D depend only on the Galois polynomial field, so they are calculated only once and can be used to expose different numbers provided that the Galois polynomial field is constant. The calculation of the number Z precedes each exposure in the Galois fields due to the fact that it depends on A.

Formally, modified as above, the Galois finite field exposure procedure using Montgomery reduction and accelerated squaring consists of the following sequence of actions:

- 1. The counter of h cycles is set in n: h = n so that it indexes the highest unit digit of the code of the exponent E.

- 2. Using the developed method of accelerated ascent to the square, the value of the square G is calculated: G = KM(G).

- 3. If the current h-th bit of the code of the exponent E is equal to one  $e_h = 1$ , then the multiplication operation with Montgomery recursion obtained in the previous step of the result G on Z: G = MM(Z, G).

- 4. The value of the cycle counter h = h-1 is decremented. If  $h \ge 0$ , then the return is performed for reexecution of claim 2.

- 5. The final result is obtained by multiplying in the Galois field using the Montgomery reduction of the obtained value of G per unit: G = MM(G, 1).

The operation of the described modified Galois field exposure procedure using the accelerated squaring based on the Montgomery reduction can be illustrated by the following example. Let it be necessary to calculate  $A^E$  rem P, and A = 12, E = 13, and the Galois field-forming polynomial has the form  $P(x) = x^4 + x + 1$ , if corresponds to the number P = 19, then n = 4. Then Montgomery technology involves the use of an auxiliary polynomial  $R(x) = x^4$ . Its multiplicative inversion  $R^{-1} = 14$ . It is easy to calculate the value  $12^{13}$  rem 19 = 8 by performing exponentiation by the classical algorithm without using Montgomery reduction.

The values  $G = R \oplus P = 16 \oplus 19 = 3$  and  $D = R|^2$  rem P = 5 are calculated in advance.  $Z = MM(A, D) = 12 \otimes 5 \otimes 14$  rem 19 = 7 is calculated immediately before the exposition.

In this paragraph 2 is the elevation to the square of the value obtained in the previous cycle G: G = KM (7) = 2. Since  $e_3 = 1$ , it is performed in paragraph 3, in which the result is multiplied by Z: G = MM (Z, G) = MM (2,7) = 11. Again subtract the unit from the counter h and return to claim 2.

When h = 2 is raised to the square of the result: G = KM(11) = 7. Since  $e_2 = 0$ , then paragraph 3 is skipped and decrements the value of the counter, resulting in h becomes equal to 1. Accordingly, the return to re-execution is realized item 2 within which the previously obtained result is squared: G = KM(7) = 2. Since the least significant bit of the exponent is equal to one, if  $e_1 = 1$ , the multiplication is performed: G = MM(Z, G) = MM(2, 7) = 11. Then decreases by one the value of h, which becomes equal to zero. This means that the exposure cycles in the Galois fields are complete. Finally, item 5 is performed – correction of the obtained result G = 11 by multiplying it by one: G = MM(G, 1) = MM(11, 1) = 8. The obtained value corresponds to the true value  $12^{13}$  rem 19 = 8.

The exposition operation consists of n cycles. In each cycle, the developed procedure of accelerated squaring to the square is performed, which is realized, on average, in  $1.5 \cdot n$  logical operations. In addition, on average,  $0.5 \cdot n$  multiplication operations are performed on Galois fields with Montgomery reduction, each of which, on average, requires  $2 \cdot n$  logical operations to implement. In general, the average number of logical operations required for exposition on Galois fields using the proposed method is  $2.5 \cdot n^2$ .

Based on the fact that in the known scheme [11] of exponentiation on Galois fields with Montgomery reduction, the average number of logical operations is  $3 \cdot n^2$  we can conclude that the proposed method can speed up the process of exposure to Galois fields by 20%, due to saving  $0.5 \cdot n^2$  logical operations. With a typical value of n = 2048 for practical applications, this is 254,000 operations. Experimental studies have shown that the real acceleration of exposure in Galois fields is in the range of 18 - 22%.

# 6. Conclusions

As a result of research aimed at accelerating the execution of the basic for a wide range of cryptographic mechanisms of the exponentiation operation in Galois fields, a new method of accelerated squaring using Montgomery reduction is proposed.

The developed method is based on the properties of a polynomial square in Galois fields and allows to reduce by 25% the number of logical operations in comparison with the use for calculation of the multiplication square in Galois fields with Montgomery reduction. Based on the developed method, a modified exposition procedure on Galois fields with Montgomery reduction is proposed. Theoretically and experimentally it is shown that the use of a modified procedure can reduce by 20% the number of logical operations and accordingly accelerate the exposure.

The proposed solutions not only speed up the calculations, but also provide their simplification, which determines their focus primarily on the hardware implementation of cryptoprocessors.

# References

- [1] M. M. Boroujerdi and S. Nazem, "Cloud Computing: Changing cogitation about computing," *World Academy of Science, Engineering and Technology*, vol. 58, pp. 1112–1116, Oct. 2009.

- [2] M. Armbrust *et al.*, "A view of cloud computing," *Commun. ACM*, vol. 53, no. 4, Art. no. 4, 2010, doi: https://doi.org/10.1145/1721654.1721672.

- [3] B. Schneier, Schneier's Cryptography Classics Library: Applied Cryptography, Secrets and Lies, and Practical Cryptography, and Malicious Cryptography. John Wiley & Sons Inc, 2007, p. 816.

- [4] O. S. Zenzin and M. F. Ivanov, *Standard of cryptographic data protection of the XXI century AES. Finite fields.* Kudic-Obraz, 2002, p. 174.

- [5] O. P. Markovskiy, Z. Leftherios, and V. R. Maksymuk, "Galois Fields Algebra Utilization for Implementation of the Conception of Zero-Knowledge Under Identification and Authentication of Remote Users," *Èlektron. model*, vol. 6, no. 39, pp. 33–46, Dec. 2017, doi: https://doi.org/10.15407/emodel.39.06.033.

- [6] M. M. Postnikov, *Foundations of Galois Theory*. Sankt-Petersburg: BXV-Peterburg Press, 2011, p. 411.

- [7] E. M. Popovici and P. Fitzpatrick, "Algorithm and architecture for a Galois field multiplicative arithmetic processor," *IEEE Transactions on Information Theory*, vol. 49, no. 12, pp. 3303–3307, doi: https://doi.org/10.1109/TIT.2003.820026.

- [8] K.G. Samofalov, O.P. Markovskyi, and A.S. Sharshakov, "The method of accelerated implementation of exponentiation on Galois fields for data protection systems," *Problems of informatization and control. NAU*, vol. 2, no. 33, pp. 143–151, 2011.

- [9] O.P. Markovskyi, S. Mehmali, and G.V. Isachenko, "Technology of digital signature DSA based on Galois Fields Arithmetics," *Herald of of National Technical University of Ukraine "KPI" Informatica, control and computer technic*, no. 55, pp. 34–41, 2012.

- [10] I.A. Kalmikov, E.S. Stepanova, and K.T. Titcherov, "Development of the method of nonlinear data encryption using an exponentiation in Galois Fields," *Modern Scientific Technologies*, no. 9, pp. 84–89, 2019.

- [11] V. Osadchyy, "The Order of Edwards and Montgomery Curves," WSEAS TRANSACTIONS ON MATHEMATICS, vol. 19, no. 25, pp. 253–264, May 2020, doi: https://doi.org/10.37394/23206.2020.19.25.

- [12] H. Wu, M. A. Hasan, I. F. Blake, and S. Gao, "Finite field multiplier using redundant representation," *IEEE Transactions on Computers*, vol. 51, no. 11, pp. 1306–1316, doi: https://doi.org/10.1109/TC.2002.1047755.

- [13] O. S. Kot and O. P. Markovskyi, "Organization of speed up exponentiation on Galois Field using Montgomery Reduction," *Almanac Science*, vol. 3, no. 36, pp. 34–37, 2020.

- [14] O. Markovskyi, V. Masimyk, and O. Kot, "The Employment of Montgomery reduction for acceleration of exponent on Galoise fields calculation," in *Proceeding of International Conference on Security, Fault Tolerance, Intelligence*, Kyiv, 2020, pp. 44–49.

- [15] G. Hachez and J. Quisquater, "Montgomery Exponentiation with no Final Subtractions: Improved Results," in *Cryptographic Hardware and Embedded Systems CHES 2000*, Koç, Çetin K and C. Paar, Eds., Berlin, Heidelberg: Springer Berlin Heidelberg, 2000, pp. 293–301.

- [16] S. Sherif Elfard, "Justification of Montgomery Modular Reduction," *Advanced Computing: An International Journal*, vol. 3, no. 5, pp. 93–96, Sep. 2012, doi: https://doi.org/10.5121/acij.2012.3510.

# OPTIMAL CONSTRUCTION OF THE PATTERN MATRIX FOR PROBABILISTIC NEURAL NETWORKS IN TECHNICAL DIAGNOSTICS BASED ON EXPERT ESTIMATIONS

In the field of technical diagnostics, many tasks are solved by using automated classification. For this, such classifiers like probabilistic neural networks fit best owing to their simplicity. To obtain a probabilistic neural network pattern matrix for technical diagnostics, expert estimations or measurements are commonly involved. The pattern matrix can be deduced straightforwardly by just averaging over those estimations. However, averages are not always the best way to process expert estimations. The goal is to suggest a method of optimally deducing the pattern matrix for technical diagnostics based on expert estimations. The main criterion of the optimality is maximization of the performance, in which the subcriterion of maximization of the operation speed is included. First of all, the maximal width of the pattern matrix is determined. The width does not exceed the number of experts. Then, for every state of an object, the expert estimations are clustered. The clustering can be done by using the k-means method or similar. The centroids of these clusters successively form the pattern matrix. The optimal number of clusters determines the probabilistic neural network optimality by its performance maximization. In general, most results of the error rate percentage of probabilistic neural networks appear to be near-exponentially decreasing as the number of clustered expert estimations is increased. Therefore, if the optimal number of clusters defines a too "wide" pattern matrix whose operation speed is intolerably slow, the performance maximization implies a tradeoff between the error rate percentage minimum and maximally tolerable slowness in the probabilistic neural network operation speed. The optimal number of clusters is found at an asymptotically minimal error rate percentage, or at an acceptable error rate percentage which corresponds to maximally tolerable slowness in operation speed. The optimality is practically referred to the simultaneous acceptability of error rate and operation speed.

**Keywords**: technical diagnostics, probabilistic neural network, pattern matrix, expert estimations, clustering, performance maximization.

# 1. Introduktion. Technical diagnostics based on expert estimations

In the field of technical diagnostics, many tasks are solved by using automated classification [1, 2]. For this, such classifiers like probabilistic neural networks (PNNs) fit best owing to their simplicity [3, 4]. Another merit is that PNNs are relatively insensitive to outliers [5]. The PNN is so simple because it is constructed easily and trained fast. Indeed, to solve a classification problem, only a pattern matrix is required. Each column in this matrix corresponds to a class (i. e., to a state of an object which is under technical diagnostics or surveillance). The elements of the column are features of the object.

To obtain a pattern matrix for technical diagnostics, expert estimations or measurements are commonly involved [1, 2, 6, 7]. Unlike other fields of diagnostics (in medicine, where a pattern matrix is obtained from images or medical tests), expert estimations are not always reliable and may contain severe biases. Similarly, measurements may be biased due to finite accuracy of tools and methodical inaccuracy. This is why every object state is estimated by at least few experts (or measurements are repeated). Subsequently, a final set of expert estimations is grouped and it can be thought of as if each expert proposes its own pattern matrix. The pattern matrix can be then deduced straightforwardly by just averaging over those expert estimations [8, 9]. However, averages are not always the best way to process expert estimations [10]. Moreover, the PNN at its input can have more than a single representative of a state (class), i. e. a few columns in a pattern matrix can correspond to the same

state. Then the PNN performance may be improved by better representing the respective states.

# 2. Problem statement

Due to the abovementioned reasons of the uncertainty of the PNN pattern matrix deduction, the goal is to suggest a method of optimally deducing the pattern matrix for technical diagnostics based on expert estimations. The main criterion of the optimality is maximization of the PNN performance. However, the subcriterion of maximization of the operation speed should be included as well because the pattern matrix cannot be "stretched" without a limit. Indeed, too "wide" pattern matrices will operate slower. For some technical fields (e. g., where diagnostics is fulfilled frequently), the operation speed is crucial, and thus the slowness will be unacceptable.

# 3. A general conception of optimizing PNNs

Denote a number of object features by F, and a number of states by S. Then the smallest possible pattern for a PNN is an  $F \times S$  matrix. Nevertheless, wider matrices can also be pattern. In general, an  $F \times (mS)$  matrix

$$\mathbf{P}(m) = \left[ p_{ij} \right]_{F \times (mS)}, \tag{1}$$

where  $m \in \boxtimes$ , can be a PNN pattern matrix. In matrix (1), each state is represented with m different patterns (columns), where  $p_{ij}$  is an assessment of feature i of the object at state s by

$$s = j - S \cdot \psi \left(\frac{j - 1}{S}\right) \text{ for } j = \overline{1, mS}$$

(2)

and function  $\Psi(x)$  returning the integer part of number  $x \in \mathbb{R}$  [11].

If there are L experts (group measurements), then  $m \le L$ . Those m different pattern matrices can be found from clustering the initial L expert matrices. Obviously, as m increases, the respective PNN operation speed may drop. So, it is necessary to determine an ultimate natural number  $m_{max}$ , at which matrix  $\mathbf{P}(m_{max})$  can be used for the pattern (the slowdown in operation speed will be hard but still tolerable), but matrix  $\mathbf{P}(m_{max}+1)$  cannot be used for the pattern due to intolerable slowdown in operation speed. This can be done by plotting (tabling) a performance time curve versus m. Instead of real pattern matrices (1) for  $m=1,2,3,\ldots$ , it is sufficient to generate random matrices of size  $F\times(mS)$  and train PNNs, whereupon the PNNs are tested (on series of vectors of F numbers, whether they are random or not).

Once a maximally possible size of the pattern matrix is determined, the respective PNNs trained on pattern matrices (1) for  $m \in \{\overline{1, m_{max}}\}$  are tested. Their performance is plotted (tabled) versus m. Then a number  $m^* \in \{\overline{1, m_{max}}\}$  at which performance is maximal is determined.

So, a general conception of optimizing PNNs is realized via three steps as follows:

- 1. To determine  $m_{max}$  ( $m_{max} \leq L$ ).

- 2. To find m clusters from those L versions of pattern matrix, for each  $m \in \{\overline{1, m_{max}}\}$ .

- 3. To determine  $m^*(m^* \leq m_{max})$ .

Nevertheless, it is worth to additionally note that selection of  $m_{max}$  can be kind of fuzzy. Furthermore, if the performance of a PNN trained on pattern matrix  $P(m^*)$  is not satisfactory, number  $m_{max}$  will be probably increased. This is expected to (at least) slightly affect the operation speed, though.

# 4. Experimental study

To model generation of the pattern matrix, it is convenient to use normal and uniform randomizers. First of all, a pivot for each state is generated. Denote the pivot value of feature i of the object at state s by  $p_i$ . So, let

$$p_{is} = \left| \psi \left( 10 \cdot \left( \xi_{is} + 1.5 \zeta_{is} \right) \right) \right|, \tag{3}$$

Where  $\xi_{is}$  is a random real number drawn from the standard normal distribution (with zero mean and unit variance) for feature i and state s, and  $\zeta_{is}$  is a random real number drawn from the uniform distribution on interval (0; 1),  $f = \overline{1, F}$  and  $s = \overline{1, S}$ .

At the second stage, the pivots are noised by similar randomizers. The noise is equivalent to inaccuracies of measurements and biases in expert estimations. The l-th version of estimation of feature i of the object at state s is

$$\overline{p}_{isl} = \left| \psi \left( p_{is} \left( 1 + \sigma_{\mathbf{P}} \xi_{isl} \right) + 1.5 \zeta_{isl} \right) \right|, \tag{4}$$

where  $\xi_{isl}$  and  $\zeta_{isl}$  are random numbers from the respective standard normal and uniform distributions,  $l = \overline{1, L}$ , and  $\sigma_{\mathbf{P}}$  is a positive factor of the noise strength. Note that values (4) of expert estimations are integer because a scale for expert estimates is commonly integer or has just a few points. Three examples of generation of pattern matrix and experts' matrices are shown in Figure 1.

| 8  | 25 | 16 | 9  | 26 | 13 | 8  | 27 | 16 | 8  | 27 | 13 | 8  | 26 | 15 | 10 | 22 | 17 | 7  | 28 | 15 |                              |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------------------------------|

| 7  | 8  | 16 | 6  | 8  | 18 | 8  | 9  | 16 | 6  | 9  | 13 | 7  | 8  | 16 | 7  | 8  | 14 | 6  | 10 | 18 |                              |

| 1  | 6  | 20 | 2  | 5  | 21 | 1  | 5  | 21 | 2  | 6  | 21 | 1  | 7  | 24 | 1  | 7  | 17 | 2  | 6  | 16 | $\sigma = 0.1$               |

| 3  | 2  | 26 | 3  | 2  | 24 | 4  | 3  | 28 | 4  | 2  | 28 | 3  | 2  | 22 | 3  | 2  | 28 | 3  | 2  | 26 | $\sigma_{\mathbf{p}} = 0.1$  |

| 25 | 10 | 10 | 21 | 10 | 7  | 29 | 10 | 11 | 26 | 9  | 10 | 27 | 9  | 11 | 30 | 10 | 10 | 29 | 10 | 10 |                              |

| o  | 14 | 9  | 0  | 15 | 8  | 1  | 4  | 11 | 0  | 8  | 11 | o  | 17 | 4  | 1  | 14 | 5  | o  | 11 | 12 |                              |

| 28 | 3  | 10 | 32 | 3  | 12 | 17 | 4  | 10 | 19 | 3  | 12 | 25 | 5  | 9  | 19 | 2  | 10 | 24 | 2  | 10 |                              |

| 1  | 0  | 3  | 1  | 0  | 2  | 1  | 0  | 3  | 1  | 0  | 3  | 0  | 1  | 4  | 2  | 1  | 2  | 2  | 0  | 3  | 0.25                         |

| 21 | 7  | 5  | 21 | 8  | 5  | 23 | 7  | 5  | 24 | 5  | 4  | 31 | 7  | 7  | 25 | 7  | 6  | 21 | 7  | 3  | $\sigma_{\mathbf{P}} = 0.25$ |

| 15 | 1  | 4  | 17 | 1  | 5  | 12 | 2  | 5  | 14 | 2  | 5  | 10 | 1  |    | 16 | 1  |    | 18 | 1  | 3  |                              |

| 4  | 25 | 5  | 2  | 19 | 3  | 6  | 30 | 6  | 3  | 14 | 3  | 8  | 53 | 9  | 7  | 34 | 4  | 1  | 27 | 4  |                              |

| 13 | 30 | 2  | 15 | 44 | 4  | 5  | 21 | 2  | 4  | 83 | 2  | 20 | 32 | 2  | 33 | 5  | 4  |    | 42 | 2  |                              |

| 25 | 21 | O  | 43 | 0  | 1  | 21 | 13 | 1  | 34 | 30 | 0  | 20 | 6  | 0  | 14 | 36 | 0  | 4  | 11 | 0  | $\sigma = 0.5$               |

| 15 | 1  | 9  | 19 | 1  | 9  | 23 | 2  | 11 | 19 | 2  | 4  | 20 | 2  | 6  | 13 | 2  | 3  | 13 | 2  | 5  | $\sigma_{\mathbf{p}} = 0.5$  |

| 26 | 5  | 8  | 36 | 5  | 5  | 32 | 9  | 1  | 26 | 6  | 0  | 30 | 4  | 19 | 57 | 2  | 1  | 8  | 10 | 12 |                              |

Fig. 1. The three examples of generating a  $5 \times 3$  pattern matrix (highlighted bold on the left) and six experts' matrices (L = 6) by increasing the noise strength factor

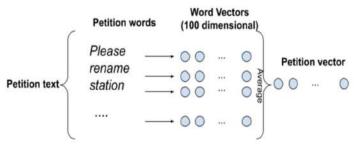

PNN pattern matrix (1) by (2) is determined as follows:

1. For every state *s* data

$$\left\{\left\{\overline{p}_{isl}\right\}_{i=1}^{F}\right\}_{l=1}^{L} \tag{5}$$

are grouped into m clusters. The clustering is done by using the k-means method [12, 13]. Consequently, m centroids of these clusters are found for every state s,  $s = \overline{1, S}$ :

$$\left\{ \left\{ c_{iks} \right\}_{i=1}^{F} \right\}_{k=1}^{m} \tag{6}$$

2. Matrix (1) is successively formed from centroids (6):

$$p_{iz} = c_{iks}$$

by  $z = s + S \cdot (k-1)$  for  $s = \overline{1, S}$ . (7)

Once pattern matrix (1) is determined, the respective PNN is trained. Then the PNN is tested using objects whose feature i at state s is

$$q_{is} = \left| p_{is} \left( 1 + \sigma_{\mathbf{p}} \xi_{is}^{(1)} \right) + 1.5 \xi_{s}^{(2)} \right|, \tag{8}$$

Where  $\xi_{is}^{(1)}$  and  $\xi_{is}^{(2)}$  are another random numbers from the standard normal distribution. It is worth to note that  $\xi_{is}^{(2)}$  implies a normally distributed shift in state s of a test object. This shift is the same for all the features. Thus, model (8) of the test object differs from model (4) of the expert estimation, in which every expert has its "own" shift distributed uniformly. Besides, unlike values (4) of expert estimations, values (8) are not narrowed to a scale or set because they model real-world objects whose features are not tied to any scale.

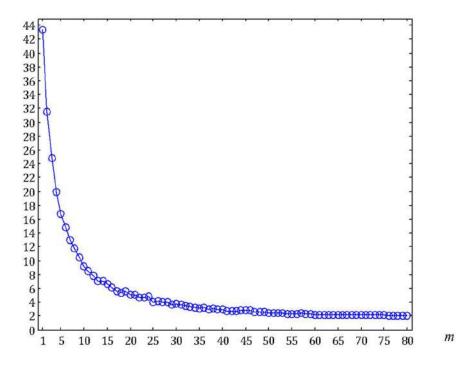

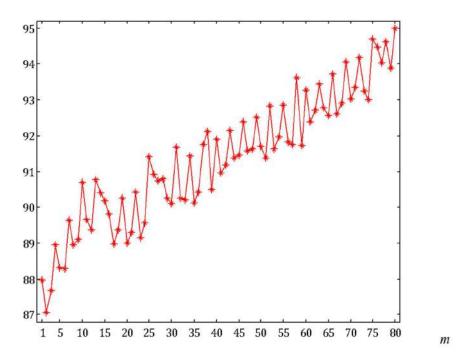

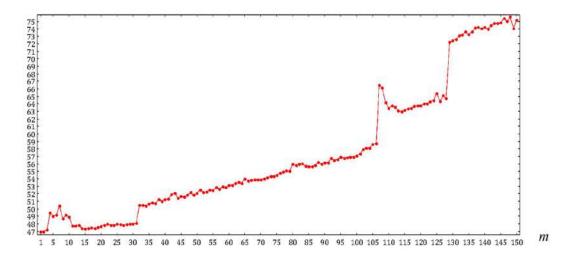

An example of diagnosing objects with seven features by four states, where 80 expert estimations are involved, is presented in Figure 2 (the PNN testing) and Figure 3 (operation speed). Figure 2 shows that the error rate percentage decreases near-exponentially as the number of clustered expert estimations is increased. Meanwhile, Figure 3 indicates that the PNN operation speed almost linearly decreases. The value of 2.095 % is an asymptotically minimal error rate percentage, and it does not change by  $m = \overline{77,80}$ . So,  $m^* = 77$  if the respective drop of the operation speed is tolerable (from nearly 87 to 94 seconds, which is about 8 %).

Fig. 2. The error rate percentage of PNNs by F = 7, S = 4, L = 80,  $\sigma_{\mathbf{P}} = 0.25$  where every object state is tested 10000 times

Fig. 3. Time (in seconds) spent on testing the PNNs by F = 7, S = 4, L = 80,  $\sigma_{\mathbf{P}} = 0.25$  (every object state is tested 10000 times)

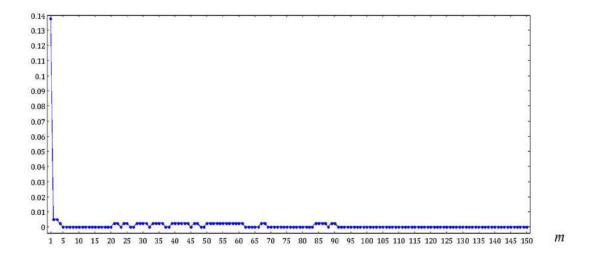

Another example, by smaller inaccuracies of measurements and biases in expert estimations, is presented in Figure 4 (the PNN testing) and Figure 5 (operation speed). By the same number of states, having just five features, these PNNs are far faster than those for objects with seven features. The zero error rate percentage (100 % accuracy) is achieved even by forming a pattern matrix as a concatenation of five cluster centroids (for each of the four states). So, in this particular case,  $m^* = 5$ .

Fig. 4. The error rate percentage of PNNs by F=5, S=4, L=150,  $\sigma_{\rm P}=0.1$  (smaller inaccuracies of measurements and biases in expert estimations than those for Figure 2), where every object state is tested 10000 times

In general, most results of the error rate percentage of PNNs appear to be near-exponentially

Fig. 5. Time (in seconds) spent on testing the PNNs by F = 5, S = 4, L = 150,  $\sigma_{\mathbf{P}} = 0.1$  (every object state is tested 10000 times), where computation speed artifacts are observed easier than in Figure 3

decreasing as the number of clustered expert estimations is increased. This also holds true by modeling expert estimations with varying  $\sigma_{\mathbf{P}}$  and other three factors in (4) by (3), and by testing PNNs with object features (8) varying  $\sigma_{\mathbf{P}}$  and the factor at  $\xi_s^{(2)}$  as well. Therefore, the example in Figure 2 is a typical performance of a set of PNNs versus the number of clusters per state.

# 5. Discussion

While the pattern matrix is determined by (5) — (7), which is the general approach, the models of expert estimations and real-world objects are made intentionally specific. In fact, expert estimations are modeled as (4) by (3), and the PNN is tested with object features (8), where only the noise strength factor  $\sigma_P$  is left loose. The specification allows adjusting the models faster owing to the specified factors are close to the best making thus the models highly sensitive (susceptible to small changes in F, S, L,  $\sigma_P$  resulting in drastic changes in the error rate percentage).

The optimal number of clusters is found at an asymptotically minimal error rate percentage, or at an acceptable error rate percentage which corresponds to maximally tolerable slowness in operation speed. However, the pattern matrix cannot be limitlessly "stretched". The optimality, therefore, is practically referred to the simultaneous acceptability of error rate and operation speed.

#### 6. Conclusion

In technical diagnostics based on expert estimations for using them in PNNs, the pattern matrix is optimally constructed by grouping the estimations for every state into the same number of clusters. The clustering can be done by using the *k*-means method or similar. The optimal number of clusters determining the PNN optimality is found by the PNN performance maximization. If the optimal number of clusters defines a too "wide" pattern matrix whose operation speed is intolerably slow, the performance maximization implies a tradeoff between the error rate percentage minimum and maximally tolerable slowness in the PNN operation speed.

The suggested optimal construction of the pattern matrix for PNNs can be applied in technical diagnostics of complex objects like devices, buildings, bridges, machines, vessels (watercrafts and airplanes), etc., based on expert estimations of the object (current) state. Apart from technical and

industrial systems, PNNs are nonetheless applicable in other domains (general engineering, social, ecological and economical systems, entertainment, surveillance), where the task is to control the state of objects whose number of features is up to a few tens or hundreds.

# References

- [1] R. Liu, B. Yang, E. Zio, and X. Chen, "Artificial intelligence for fault diagnosis of rotating machinery: A review," *Mechanical Systems and Signal Processing*, vol. 108, pp. 33–47, 2018, doi: https://doi.org/10.1016/j.ymssp.2018.02.016.

- [2] H. Czichos, Ed., *Handbook of Technical Diagnostics*. Berlin, Heidelberg: Springer Berlin Heidelberg, 2013. doi: https://doi.org/10.1007/978-3-642-25850-3.

- [3] T. Masters, "Probabilistic Neural Networks," in *Practical Neural Network Recipies in C++*, San Francisco (CA): Morgan Kaufmann, 1993, pp. 201–222. doi: https://doi.org/10.1016/B9780080514338.500173.

- [4] A. Annema, *Feed-Forward Neural Networks*. NY: Springer New York, 1995. doi: https://doi.org/10.1007/978-1-4615-2337-6.