# **UDC 004**

Information, Computing and Intelligent systems. – 2022. – № 3. – P. 112.

Recommended for publication by the Academic Council of the Faculty of Computer Science and Computer Engineering

Sergii Stirenko *Editor in Chief:* Deputy editor in Chief: Iryna Klymenko Responsible secretary: Liudmyla Mishchenko *Editor board:* Sergii Telenvk Mikolaj Karpinski Nikolai Stoianov Inna Stetsenko Oleksandr Rolik **Oleg** Chertov Yuri Gordienko Anatoliy Sergiyenko Michail Novotarskiy Yurii Kulakov Oleksiy Pysarchuk Oleksandr Markovskvi

The scientific journal "Information, Computing and Intelligent systems" is intended for the publication of the results of scientific research and scientific and practical developments in the field of technical sciences by students, masters, PhDstudents, scientists, and practicing specialists in the field of science "Information systems".

The thematic orientation of the journal "Information, computing and intelligent systems" is reflected in the following headings: computerized and computer systems and networks, information technologies, the Internet of Things, information transformation and processing, cloud computing, computer cryptography, data protection, intelligent systems, artificial intelligence, machine learning, automated design of software and technical tools, system control, diagnostics and control of parameters of complex systems, processes and environments; engineering knowledge, embedded systems, robotics, microelectronics.

ISSN 2708-4930

Certificate of state registration No. 23827-13667∏P from 20.02.2019 Magazine in English Web- resource – https://itvisnyk.kpi.ua/ Format 60×84 1/8. Garnitura Times. Offset Folder № 1.

© National Technical University of Ukraine "Igor Sikorsky Kyiv Polytechnic Institute", 2022

SCIENTIFIC EDITION

# Information, Computing and Intelligent systems

The journal is the legal successor of the Collection of scientific works "Bulletin of NTUU "KPI". Informatics, control and computer engineering"

Founded in 1964 years

Issue 3

Kyiv – 2022 (3)

# SUMMARY

| <i>A. Sergiyenko, P. Serhiienko, I. Mozghovyi, A. Molchanova</i> Design of data buffers in field programmable gate arrays                                                      | 4   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Al-Mrayt Ghassan Abdel Jalil Halil, O. Markovskyi, A. Stupak Organization of fast exponentiation on galois fields for cryptographic data protection systems                    | .17 |

| I. Boiarshyn, O. Markovskyi, B. Ostrovska Organization of parallel execution of modular multiplication to speed up the computational implementation of public-key cryptography | .26 |

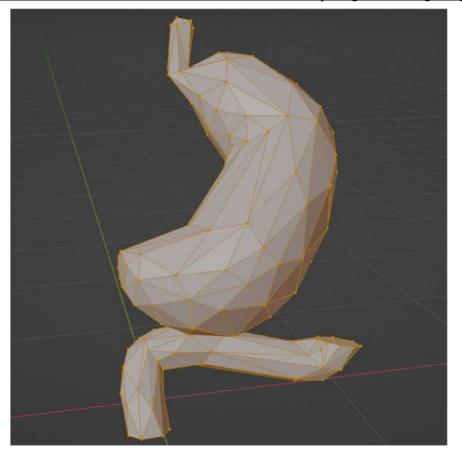

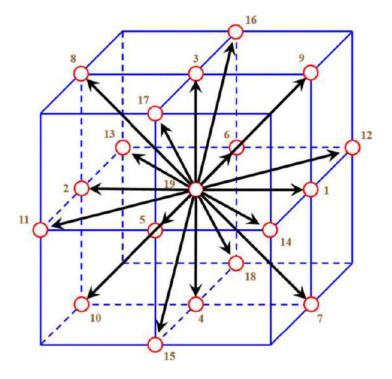

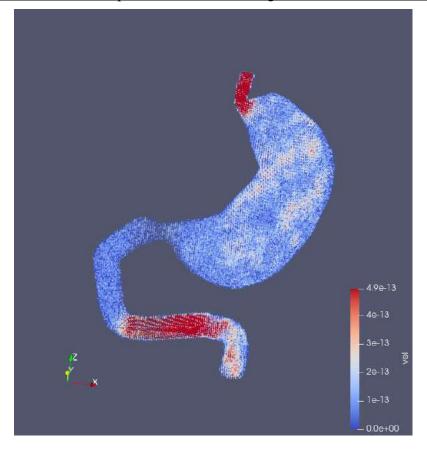

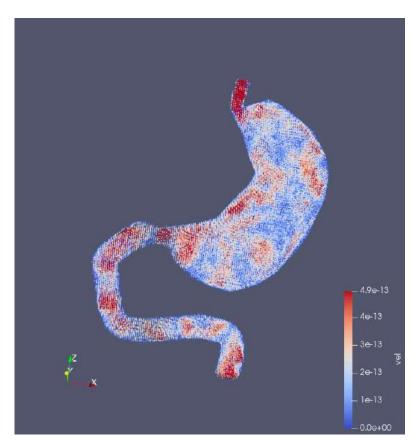

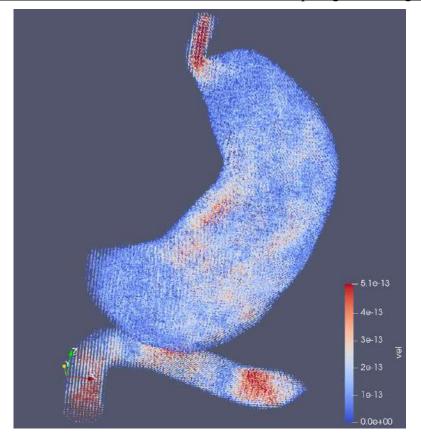

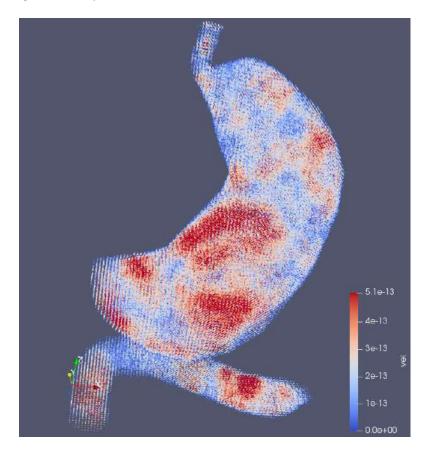

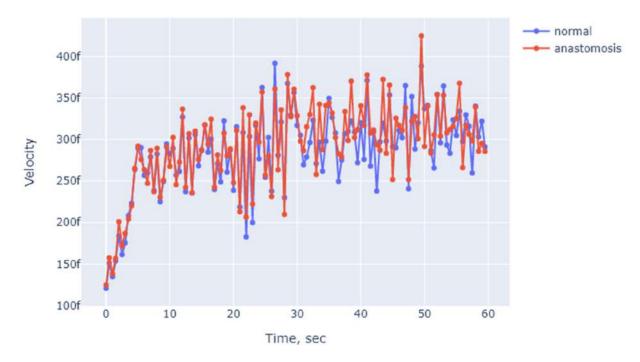

| <i>V. Kuzmych, M. Novotarskyi</i> Simulation of fluid motion in complex closed surfaces using a lattice boltzmann model                                                        | .33 |

| I. Daiko, V. Selivanov, M. Chernyshevych, O. Markovskyi Zero-knowledge identification of remote users by utilization of pseudorandom sequences                                 | .42 |

| A. Mirataei, O. Rusanova, K. Tribynska, O. Markovskyi Organization of protected filtering of images in clouds                                                                  | .49 |

| A. Mirataei, M. Haidukevych, O. Markovskyi Fast secure calculation of the open key cryptography procedures for iot in clauds                                                   | .56 |

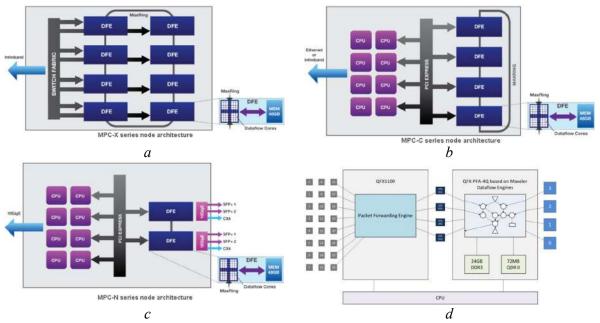

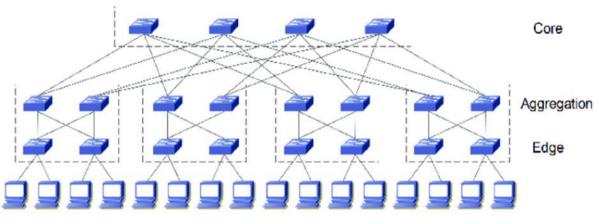

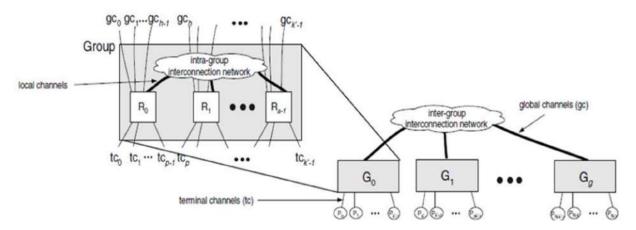

| O. Honcharenko, H. Loutskii Methods of effectivization of scalable systems: rewiew                                                                                             | .63 |

| A. Verner, I. Klymenko Modern information systems security means                                                                                                               | .77 |

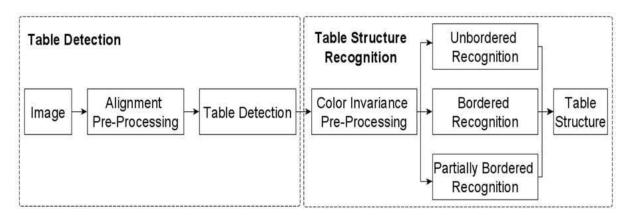

| O. Yaroshenko Overview of ocr tools for the task of recognizing tables and graphs in documents                                                                                 | .87 |

| Abstracts                                                                                                                                                                      | .95 |

| Анотації                                                                                                                                                                       | 104 |

# **DESIGN OF DATA BUFFERS IN FIELD PROGRAMMABLR GATE** ARRAYS

# A. Sergiyenko, P. Serhiienko, I. Mozghovyi, A. Molchanova

The design of the data buffers for the field programable gate array (FPGA) projects is considered. A new method of buffer design is proposed, which is based on the representation of the synchronous dataflow graph in the three-dimensional space, optimization of them, and description in VHDL. The method gives the optimized buffers which are based either on RAM or on the register pipeline. The derived pipeline buffer can be mapped into the shift register primitive of FPGA. The method is built in the experimental SDFCAD framework intended for the pipelined datapath synthesis. *Keywords*: *FPGA*, *VHDL*, *synchronous dataflow*, *datapath synthesis*.

#### Introduction

Field programmable gate arrays (FPGAs) are popular devices that provide both high-speed computations for any complex task and availability for many designers of application-specific computers. The FPGA design technology was expanded over the last decades, which is based on the register transfer level (RTL) description of the computational datapath using the hardware description language like Verilog or VHDL. In recent years, high-level synthesis tools become popular because they provide a compilation of the C programs into the hardware descriptions, inviting the firmware programmers for designing the FPGA applications [1].

In many cases, the FPGA project consists of a set of ready blocks and intellectual property cores (IP cores) that communicate with each other through the proper interfaces and data buffers. But the selection of these interfaces and designing these buffers are still uncertain. In most cases, the usual methods of the RTL design are used or the ready IP cores are selected to build the data buffers, which gives the increased hardware volume, insufficient throughput, or both.

Most FPGA projects are pipelined, application-specific processors. The FPGA architecture contains a lot of hardware resources like registers, FIFOs, pipelined DSP blocks, two-port blocked RAMs (BRAM), and pipelined input-output pads, which support the pipelined computations. But they are utilized in the data buffers using the old synthesis methods which don't provide good results. In particular, the buffers are usually designed separately from the pipelined datapath to which they are connected [2].

In the article, a new method of data buffer design is proposed which provides effective FPGA resource utilization. The derived buffer solution is described by the VHDL language and can be used effectively in any hardware project.

## Methods for the buffer design

The methods of the data buffer design evolved for decades. The memory bandwidth increase is the usual goal of the buffer design. The easiest way to increase the memory bandwidth is to have multiple memory blocks in parallel. Similarly, it is possible to implement a memory with an extralarge data word length that stores several adjacent data. But in these cases, when the memory is out of FPGA, in addition to several memory chips, it is necessary to have many separate outputs from FPGA for addresses and data, which is often unacceptable. The impact of this problem is somewhat reduced by organizing several blocks of cache memory in FPGA. By dividing the address space into multiple banks, using one memory bank for odd addresses and another one for even addresses, the adjacent addresses can be accessed simultaneously. For example, four banks can be used to access four pixels in a 2×2 block. In addition, for efficient access to the pixels in the aperture, the address can be coded as proposed in [3].

In the pipelined random access to RAM, one process can write results to one memory bank, and another can read data from the second bank. When the processing of the next data array is completed, the banks switch their roles. At the same time, a third memory bank is used for better synchronization [4]. But such switching of banks adds a long period of time to the latency of the algorithm and has the consequence of increasing the hardware costs of the system, and the use of more FPGA pads.

A more practical approach is to run the memory at a higher clock frequency than the rest of the system. Double data rate (DDR) memory is one example of memory that allows data to be transferred twice per clock. As a rule, modern high-capacity FPGAs have dedicated outputs and a built-in access controller for external dynamic DDR memory of recent generations [5]. At the same time, the project simulates multiport memory due to access time slots. In addition, blocks of the buffer memory are required for writing and reading, since dynamic memory has high throughput only when transferring rows of data from neighboring cells. Unfortunately, in many projects, DDR memory is also required to support the operating system of the processor embedded in the FPGA, and therefore the bandwidth of this memory drops when processing large data arrays.

Pipeline and FIFO first-in-first-out (FIFO) type buffers are two popular types of memory organization methods utilized in FPGA. They are distinguished in the following. The data stored in and retrieved out of a pipeline is also in the first-in-first-out category. But the steps of storage and retrieval are constant as in the serial-in-serial-out shift register. A FIFO buffer is a storage where the data can be pushed into and popped out with the same data order, but these operations can be uncorrelated. However, the implementation of both long pipeline buffer and FIFO is based on RAM which is operating as the circular buffer. The method of such buffers design is explained in [6]. But the designer must organize the proper order of data pushing and popping separately.

If the data are executed sequentially, then it is worth using the buffers of the FIFO type, which cell groups store blocks of data, and the output data are selected by the local addresses [7].

When the algorithm can be represented by some Petri net, then the stream processing computational model can be used. In this model, the computational node or processing kernel consists of the stencil buffer and computing module connected to the buffer inputs. During the computational process, the input data are loaded into the buffer asynchronously and just when they form the proper stencil the computations start [8]. So, the buffer is really the register pipeline with a large set of outputs, which is often the inefficient solution.

When the usual serial program is mapped in the hardware, then the data buffer with the last-infirst-out discipline is needed. The method of such stack buffer design as well as the respective finite state machine development named Hierarchical Finite State Machines (HFSM) method is described in [9].

The von Neumann architecture paradigm is widely used in which each datum has its own robust address in the common address space. The data buffers are implemented as the cache memory blocks in this paradigm. Note, that in particular, when the data lose their addresses in the moment before their execution, then this cache memory can be represented as a usual FIFO buffer. Therefore, the usual data buffer is often called the cache [10]. The method of the cache buffer design for FPGA based on the optimized data throughput is described in [11]. When the FPGA application deals with dynamic memory allocation, then the cache buffers can be designed using the method of algorithm analysis which selects the independent and shared memory fields [12].

The dataflow processing is the kind of algorithm that is usually implemented in FPGA because the FPGA architecture provides the effective implementation of such algorithms. The most common model for the dataflow algorithm representation is the Kahn processing network (KPN). The nodes of this network represent the operations or actors, and the edges represent the dataflows. The edges contain the FIFO buffers of the proper length. Usually, KPN is mapped into FPGA by one-to-one mapping. So, the FIFO buffers serve as the proper data buffers [13]. Note, that this model considers that the data are retrieved from FIFO in arbitrary order, i. e., the buffer can contain several outputs from its head registers.

The unified modeling language or UML provides an effective KPN representation. Many tools like IBM Rational Rhapsody provide translation of the UML description into hardware [14]. The Matlab Real-Time Workshop (RTW) tool offers code generation capabilities directly from Simulink graphical system descriptions which is a kind of KPN [15]. These tools implement the FIFO buffers as they are foreseen in the given KPN. But these buffers must obey the rules of the asynchronous reading and writing data in them in the respective order.

The synchronous dataflow (SDF) graph is the abridged KPN model, in which all dataflows are synchronous. Note, that two dataflows are synchronous if the data in one flow are correlated with the data in the other one, for example, both data samples have the same index sets. The FIFO buffers in the SDF model are always synchronous ones, and this model is usually free of deadlocks. This model gives simple mapping to hardware, providing effective methods of structure optimization like pipelining, retiming, folding, and resource sharing [16]. This idea is expanded and fulfilled in the SDF modeling framework Ptolemy [17]. By this method, the optimized data buffers are synthesized as well. But the synthesis results can be far from excellent because the optimization is performed by hand or automatically. Through this process, the effective schedule is searched which disagrees with the hardware minimization.

When the algorithm given by SDF has no loops and feedback then it is usually represented by the dataflow graph (DFG). Then, the data buffers with the minimum volume can be synthesized using the method proposed in [18]. This method combines the register allocation by the left-edge scheduling and the SDF folding.

When the 2D signals or images are processed, then the problem of the buffer design becomes more complex. In this situation, the multidimensional SDF can be used, in which the data have the vectors of indexes which can be considered as the pixel coordinates in the image frame [19]. But the buffer design remains a complex task.

Many algorithms including ones of image processing are represented by the loop nest. The index vectors of the loop nest iterations and the data themselves form the multidimensional grid, and the algorithm does the respective lattice-like DFG. The method of the systolic processor design is widely used for mapping these algorithms both into the processor structure and into the timetable of the operator execution [16]. The pipelined data buffers are the obligatory result of such mapping. Therefore, this method is widely used now to design data buffers in many synthesis methods and automatic design frameworks.

Placing the operators in the iteration space and mapping them in the structure and timetable is used in [20] as well. To optimize the data buffers, the system of linear inequalities which takes into account the operator data dependencies, data moving delays, and time limitations. This system is solved using the usual integer linear problem solver. As a result, the throughput is optimized and the pipelined data buffers are synthesized. But the synthesis process becomes very complex when the problem dimension increase.

This method is expanded using the polyhedral model of the parallel algorithm DFG representation and its mapping [21]. Due to this method, the executed iterations of the algorithm and their data form the polyhedron in the multidimensional iteration space which limits the volume of the lattice-like DFG. Each iteration in it occupies a particular integer vector in the space. This polyhedron is mapped into the systolic structure of the computer and the timetable using the optimized affine transformations of this space. When the loop nest describes the data array behavior then the result of the mapping is a set of pipelined data buffers. A similar method is proposed in [22]. The method named lattice-based partitioning is based on the same principle and performs the selection of a set of distributed buffers [23].

FPGA hardware is utilized very well providing high throughput when the data are reused frequently. The method of the buffer design described in [24] provides the data reusing when the algorithm performs the sequential array processing using the modulo addressing. A more sophisticated method utilizing data reuse is proposed in [25]. The approach of the systolic processor design is implemented in it and the data which are fetched from the one- or two-dimensional array are reused in the algorithm.

The buffers of different lengths should be designed for different data array sizes. It is proposed to use a universal buffer, which is adjusted to the array size and the computed frame in it with the possibility of dynamic reconfiguration [26]. A similar method for image processing is described in [27], which is capable of transposing the position of pixels in the frame, as well as performing image correction at the frame edges.

The works [28, 29] present general methods of designing a pipelined structure for image processing with a sliding aperture selected for processing. At the same time, the functions that are

sequentially performed in the algorithm are mapped in the corresponding processing blocks, which are separated from each other by buffer blocks that store several adjacent lines. The interconnections between processing blocks and buffer blocks are buses that correspond to the edges of DFG.

The smart buffer is a compiler-generated data buffer that provides re-using the fetched data in the sliding aperture. The structure of the buffer is determined by the window size, array size, and the stride of the reuse in each dimension [30]. This method is effectively utilized in the Riverside optimizing compiler for configurable computing (ROCCC) approach and compiler [31].

#### Goals of the investigation

The analysis of different methods of the data buffer design makes it possible to conclude the following.

KPN mapping gives a set of pipelined data buffers in a natural manner. However, the resulting buffers have several output ports in many cases and the deadlock problem is solved hard.

SDF is the abridged model of KPN, but it is a rather impressive one and it is free of deadlocks. Many dataflow algorithms like digital signal processing are represented as SDF and are effectively mapped into hardware structures including pipelines and FIFOs.

The most sophisticated and formalized methods are ones that are based on the representation of the algorithm as DFG in the multidimensional grid and mapping it into the systolic-like processor structures. Many of them are implemented in high-level synthesis frameworks. But these methods are limited by the algorithms which are represented by the loop nests and do not take into account the features of the hardware technology.

The goal of the investigation is to develop a new method of data buffer design that is more sophisticated and is able to take into account the features of the FPGA architecture. The method is intended for the pipeline buffer design however it is fitted for the buffers based on RAM. These buffers are designed in general for the streaming algorithms like DSP, image processing, or others that can be represented by SDF.

The derived buffers must be optimized both in the clock frequency and in hardware. Therefore, first of all, the FPGA features are considered. Then, the method of the pipelined datapath design is selected which involves the better features of the methods considered above. And next this method is adapted to the data buffer design.

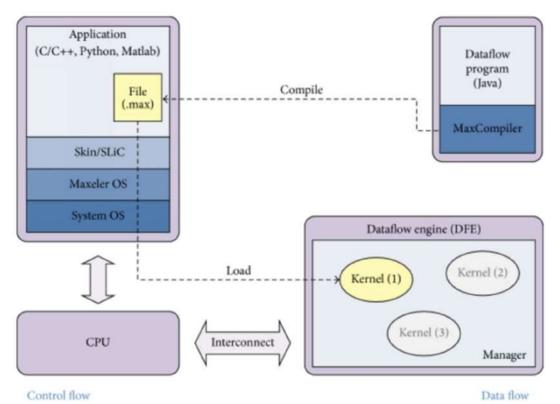

## FPGA resources for the buffer design

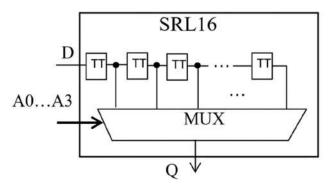

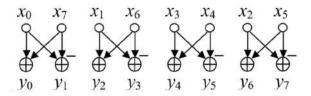

The FPGA chip usually contains sufficient volume of different memory resources. Usually, the basic building block is the Look-Up Table (LUT) in Xilinx FPGAs or Adaptive Logic Module (ALM) in Intel FPGAs. Each of them is accompanied by one or two 1-bit registers. These registers usually form the storage elements of the pipeline stages including the pipeline buffers. LUT by itself is configured as the buffer RAM with a volume of up to 64 bits, and with several possible reading ports. Moreover, it can be configured as the pipeline buffer of the variable length. Fig. 1 illustrates the structure of such an SRL16 primitive which contains the 16-bit shift register, and each of its taps is selected statically or dynamically by the output multiplexor.

Fig. 1. Pipeline buffer SRL16 structure

FPGA contains from tenths to thousands of two-port blocked RAMs (BRAMs). Each of them contains kilobytes of memory of programable bit width. The ratio of BRAM number to LUT number in FPGA is equal from 60 to 200. Usually, they can be configured as FIFO buffers [32, 33].

The Intel Hyperflex FPGA architecture provides the pipeline buffers of the arbitrary length in the routing segments in the inter ALM communications. These buffers enable the highest clock frequencies in Intel Stratix® 10 and Intel Agilex<sup>TM</sup> devices [34].

Usually, the most effective structure solutions are derived from the register transfer level (RTL) design. But in such a design, the buffer selection, and its dynamic control, which depends on the modules attached to it, is a hard design task. Therefore, the usual solution is selection the FIFO buffer based on BRAM, which takes increased hardware volume. The SRL16 buffers are utilized rarely in some specific finite state machines (FSMs), filters, or encryptors [35]. The Hyperflex register utilization in the projects takes specific knowledge about the SDF optimization and is not fulfilled in most cases when SDF contains the loops [34].

#### **Spatial SDF method**

A method of designing the pipelined datapaths by mapping SDF is proposed in [36, 37]. The feature of the method is that SDF is represented in the resource-time space in the form of an algorithm configuration (AC). The method makes it possible to search for a schedule, minimize the number of processor units (PUs), and search for effective interprocessor connections simultaneously. Here, PU means an elementary computing element with or without result registers, for example, an adder, a multiplier with a register, a pipeline buffer, etc. Therefore, it makes sense to create a method for the data buffers development based on this method. It is described below in short.

At the first stage of the synthesis, according to the specified method, operators-nodes of a homogeneous SDF together with the data dependency edges are located in three-dimensional space  $\mathbb{Z}^3$  as sets of vectors  $K_i$  and  $D_j$ , respectively, taking into account the conditions, given in [36]. The coordinates of the vector  $K_i = (s, q, t)^T$  mean the number *s* of the PU, where the operator is executed, the type *q* of this PU, and the time component *t*, which is equal to the clock number during the execution of the algorithm. Vectors  $K_i$  with equal time components form one row and are executed simultaneously. The time component  $R(D_j)$  of the vector  $D_j = K_i - K_l$  is equal to the delay between the executions of operators whose nodes  $K_i$ ,  $K_l$  are adjacent. The number of PUs is minimized by fulfilling the requirements  $|K_{s,q}| \rightarrow L$ , i.e. the number of nodes mapped in the *s*-th PU approaches to *L*, where *L* is the algorithm execution period in clock cycles. In addition, when forming the effective algorithm configuration, it is desirable to build a perfect spanning tree of SDF, as suggested in [38].

In the second step, AC is balanced, which consists in adding delay nodes to the edges of SDF until the time components of all vectors  $D_j$  are equal to 0 or 1. After that, AC is optimized by permuting the node vectors from the same column in order to minimize the number of registers and the number of multiplexer inputs in the resulting structure and/or using other strategies, for example, retiming. Also, the number of registers is minimized by gluing delay nodes from the same column that store the same operand.

In the third step, the obtained optimized AC is mapped in the graph of the computer structure in the subspace  $\mathbb{Z}^2$  named as the structure configuration. This is done by gluing the node vectors with the same coordinates *s*, and *q*. AC is transformed into the schedule of operator execution, using the property that the time component of the vector  $K_i$  is equal to the moment of execution of the operator, regardless of the number of the execution period. At the same time, the resulting structure is not built and the schedule is not formed because the resulting structure is described in VHDL on the base of information in AC.

#### Method for the buffer design

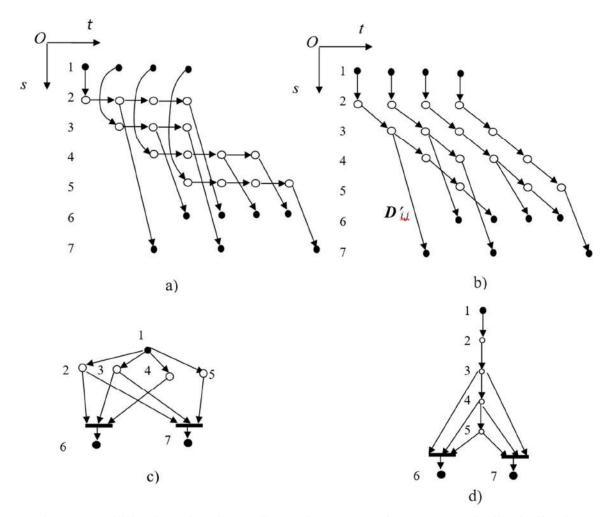

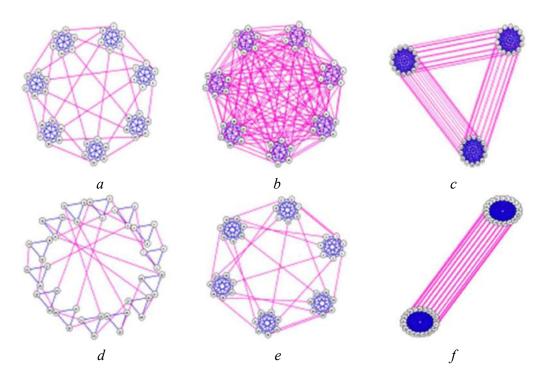

Consider AC  $C'_{A\nu}$  which performs the iterative algorithm with the period of L = 4 clock cycles, and which consists only of input and output nodes. This AC is mapped into the data buffer. When placing the nodes of CA in the space  $\mathbb{Z}^3$ , one should use some strategies to minimize the number of connections between PUs. The location of the nodes of the delay operators according to the strategy of placing the edges  $D_{i,j}$  in parallel to the axis *Ot* in the second step of the synthesis is shown in Fig. 2,

a. And the configuration  $C'_{Av}$  according to the strategy of placing the edges  $D_{i,j}$  at an angle to the axis Ot is shown Fig. 2, b. The structure configurations corresponding to these CAs are shown in Fig. 2, c, and 2, d, respectively. Here, the bold points mean the nodes of input-output or some operator nodes, and circles mean the delay nodes mapped into the registers. The bars mean the multiplexers attached to the PU inputs, which perform the selection of the operand when it is read from the respective register.

Fig. 2. AC which edges placed according to the strategy of RAM (a) or pipeline buffer (b) synthesis, and respective RAM (c) and FIFO (d) configurations

Analysis of these structure configurations shows that they correspond to two-port RAM (one port to read-write, second one only to read) and pipelined data buffer, respectively. Applying one or another strategy of connection number minimizing, the designer can orient the process of synthesis of the data buffer to implementation in the form of RAM or a register pipeline. The strategy should be chosen taking into account the following features.

When synthesizing the buffer based on RAM, the variable  $x_i$  is allocated in the respective register, i.e. the chain of delay nodes is located on a straight, which is parallel to the axis Ot. Also, one register is assigned to several variables whose periods of existence do not overlap, i.e. several chains of delay nodes are located on a straight, which is parallel to the axis Ot, and these chains do not overlap. At this process, the edges  $D_{i,j}$ , which are adjacent to the outputs of the edges  $K_{i,j}$  of the AC before balancing the relation

$$\max_{i:i}(t_{\mathrm{D}i,j}) \le L \tag{1}$$

is satisfied, where  $t_{Dij}$  is the time component of the vector-edge  $D_{ij}$ . If it is not observed, it is necessary to cut the balanced AC  $C'_{A\nu}$  into several subconfigurations, each of which will corresponds to its own

RAM or ensure overwriting of the variable  $x_i$  for which it is not observed the inequality (1), in the second register of the RAM after *L* clock cycles. It is obvious that the volume of the resulting RAM for AC C'<sub>Av</sub> with  $\lambda$  input nodes (bold points in Fig. 2) is equal to

$$N_{\rm P} = \lambda. \tag{2}$$

When the pipeline buffer is designed, then the variable  $x_i$  is sent to the adjacent pipeline register in each clock cycle and, passing through a chain of  $t_{Di,j}$  registers is outputted from it to the input of PU which receives this variable. This is equivalent to the fact that the chains of adjacent nodes  $K_{i,j}$  of the delay operators at uniformly increasing coordinates  $s_{i,j}$ , and  $t_{i,j}$  are placed along parallel lines, located at an angle to the axis Ot (Fig. 2, b). Therefore, the value of  $t_{Di,j}$  in (1) can be any, however, to minimize the number of the register pipeline stages, the number of different values of the vectors  $D'_{i,j}$  must be minimal. The number of registers in the pipeline is equal to

$$N_{\rm P} = \max_{i,i}(t_{{\rm D}i,j}). \tag{3}$$

Thus, AC which performs the data transfer between input and output ports after its balancing and optimization according to one of two strategies gives a minimized amount of memory in the resulting data buffer. We get a buffer structure with memory organized in the form of RAM or a register pipeline. At the same time, the number of registers in RAM is smaller than in the pipeline of registers, if the number of input nodes that are mapped to one port node (the number of different variables entering one PU) in AC is less than the maximum delay of the variable that is calculated in this PU, i.e. at

$$\lambda = \max(t_{\mathrm{D}i,j}). \tag{4}$$

When the resulting pipelined buffer is performed in the SRL16 primitive, then the method must take into account the fact that it has a single output (see Fig. 1). This adds the additional limitation to AC placement in the space that only a single edge must connect any delay node with the node which is mapped into the output port PU. AC in Fig. 2, b does not satisfy this condition. Therefore, it is split into two subconfigurations in Fig 3, a, which satisfies it and is mapped into the structure with two units implemented in SRL16 primitives (Fig 3, b).

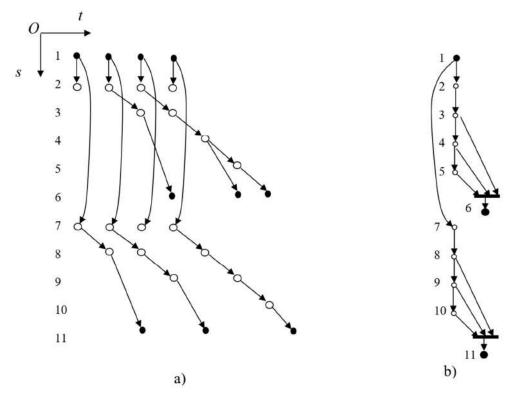

The SRL16 primitive has an additional clock enable input, the control of which makes it possible to slow down the data moving through the pipeline registers. When using this input, the number of registers can be minimized if the value of  $R(D_j)$  is greater than the number of available registers in the pipeline. Fig. 4 shows an example of the transformation of AC, shown in Fig. 3, a, for the purpose of additional delay of the operands. Such delays correspond to the vectors  $D_j$ , which are placed parallel to the axis *Ot*. Note, that the number of nodes that have the same coordinate *s* must not be higher than the computation period *L*.

The Fig. 4 analysis shows that the technique of the clock enable control allows us to minimize both the pipeline register number and output multiplexers substantially. This is important when the pipeline registers are performed on the base of usual registers because it saves hardware and minimizes the clock period.

If the nodes-sources of considered AC have different spatial coordinates s (in the examples above s = 1), then an input multiplexor is obtained at the input of the SRL16 primitive. To minimize such multiplexers, the method can be used which is described in [39].

Thus, the method of designing the pipelined datapaths with buffers based on SRL16 primitives looks like the following. The initial data are AC, algorithm execution period L, and other optimization parameters. The method is performed in the same way as described in [37, 38], with the exceptions described below.

In the first stage of synthesis, the AC subgraphs corresponding to the transfer of operands between computer resources with time delays and/or shuffling of operands, which are expected to be mapped into separate data buffers, should be selected.

Fig. 3. AC which is split to AC in Fig. 2, b (a) and its mapping into SRL16 structures (b)

In the first stage of synthesis, the AC subgraphs corresponding to the transfer of operands between computer resources with time delays and/or shuffling of operands, which are expected to be mapped into separate data buffers, should be selected.

Fig. 4. Modified AC Fig. 3, a (a), and its mapping into SRL16 structures (b)

In the second stage, it is necessary to balance the dependence edges using the intermediate delay nodes. The number of intermediate delay nodes is minimized, if possible. The delay nodes are placed on parallel lines that are at an angle to the time axis or parallel to this axis in such a way that adjacent delay nodes differ in time coordinates by one beat. The requirements for the correct placement of nodes are fulfilled, including the requirement to implement a buffer with one input and one output. If it is impossible to get a single input in the buffer, the heuristic of minimizing the number of inputs of the additional multiplexer at the buffer input is used according to [39], and if it is impossible to receive a buffer with one output, the chain of delay nodes is split so that they are mapped in additional buffers (see Fig. 4).

The dependency edges together with the corresponding delay nodes which are incident to the nodes consuming the buffered data should be mapped in the data buffer. When a control algorithm is designed, if only edges are displayed in the buffer that is at an angle to the time axis, then operands are written to the buffer in each clock cycle. If there are edges that are parallel to this axis, then writing to the buffer is prohibited in the corresponding clock cycles (see Fig. 4).

At the third stage, the pipelined datapath is described in VHDL according to the method presented in [38] and is compiled into an FPGA configuration that contains the buffers based on SRL16 primitives, which correspond to the selected AC subgraphs.

#### **Experimental results**

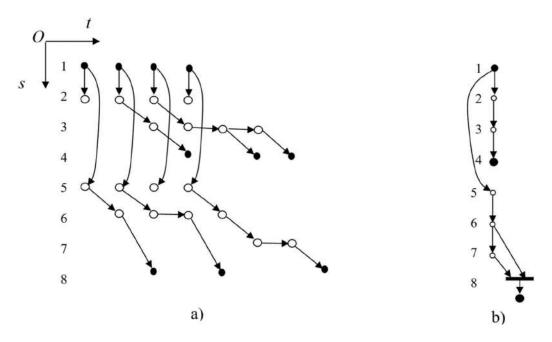

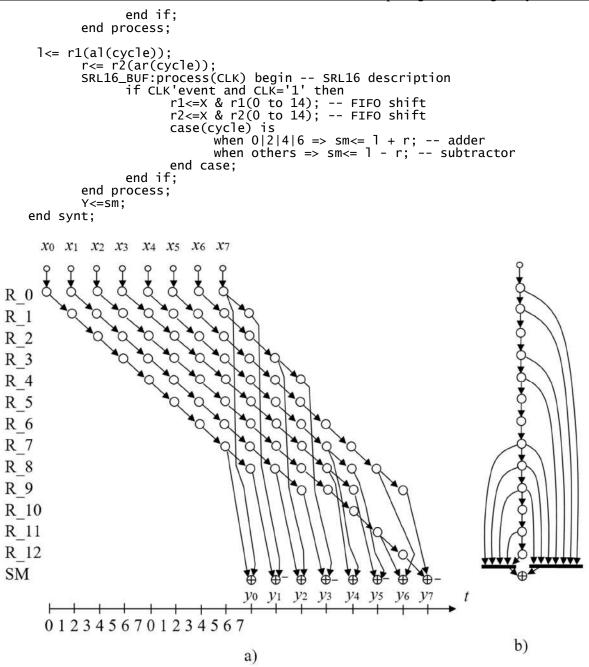

Consider the design of the input buffer for the pipelined datapath performing the 8-point discrete cosine transform (DCT). The DFG of this algorithm is often based on the Chen algorithm [41]. This algorithm is distinguished in that its period of the pipelined computations is equal to L = 8 clock cycles, eight input data of a single DCT transform need to be delayed and permutated in the input buffer before their calculations. DFG of the first stage of this algorithm which needs the data buffer is shown in Fig. 5.

Fig. 5. DFG of the first stage of the DCT algorithm

Optimized AC which is mapped into pipelined buffer and adder, and respective structure configuration are illustrated in Fig. 6. Here, the resource names are placed in the Os axis and the clock cycle number modulo L = 8 is mapped in the axis Ot. The addition-subtraction operator node has the plus sign. This AC is described in VHDL as follows.

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.Numeric_STD.all;

entity DCT_BUF is

port(

CLK : in STD_LOGIC;

RST : in STD_LOGIC;

START : in STD_LOGIC;

X : in SIGNED(8 downto 0);

: out SIGNED(8 downto 0)

):

end DCT_BUF;

architecture synt of DCT_BUF is

type TARRAY16 is array (0 to 15) of SIGNED(8 downto 0);

type TN is array(0 to 7) of natural range 0 to 15;

constant al: TN:=(7,8,8,9,8,9,11,12);

constant ar: TN:=(0,1,3,4,7,8,8,9);

signal r1 r2:TAPPAY16: -- register array of col16

signal r1,r2:TARRAY16; -- register array of SRL16

signal cycle:natural range 0 to 7;

signal sm,1,r: SIGNED(8 downto 0);

begin

CT8:process(CLK) begin -- period counter

if CLK'event and CLK='1' then

if START='1' then

cycle<=0;

else

cycle<= (cycle+1) mod 8;

end if;

```

Fig. 6. Balanced spatial SDF for DFG in Fig. 6 (a), and respective structure configuration (b)

Here, signals r1, r2 represent two pipeline register chains, which load the input data X in each clock cycle. They are synthesized after splitting AC in Fig. 6, a in two subconfigurations like it is done in Fig. 4. The signals from them *l*, *r* are read at addresses which are sampled from ROMs *al*, *ar*. These signals are directed to the left and right inputs of the adder-subtractor with the register *sm* deriving the result *Y*. The calculating period counter cycle counts modulo L = 8 and controls both the sign of the adder *sm* and the pipeline register chains through the ROMs *al*, *ar*.

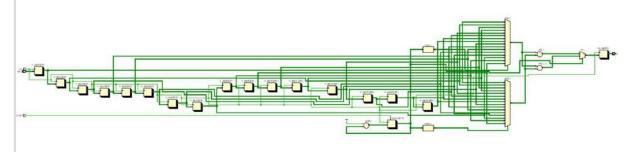

This project is compiled by the Xilinx ISE and Vivado CAD packages into FPGAs of different series. The results of compilations are shown in Table 1.

This table analysis shows that the ISE synthesizer recognizes the template of the SRL16 primitive and the synthesis results are the data buffers with the minimum hardware volume and good performance. The Vivado synthesizer first tries to compound both pipeline buffer branches into one and then minimizes the trigger number by substituting the chains of registers with the SRL16 primitives. The inferred structure is illustrated in Fig. 7. One can see, that additionally, the synthesizer

doesn't perform the resource sharing of the adder-subtractor. As a result, the hardware volume in the register number is much higher.

| FPGA<br>series | Compiler   | Slice Flip<br>Flops | LUTs | LUTs used<br>as logic | LUTs used<br>as SRL16 | Minimum clock<br>period, ns |

|----------------|------------|---------------------|------|-----------------------|-----------------------|-----------------------------|

| Virtex-4       | ISE 14.7   | 12                  | 37   | 19                    | 18                    | 3.14                        |

| Spartan-3A     | ISE 14.7   | 12                  | 37   | 19                    | 18                    | 5.47                        |

| Spartan-6      | ISE 14.7   | 12                  | 39   | 29                    | 10                    | 4.72                        |

| Artix-7        | Vivado2016 | 111                 | 44   | 39                    | 5                     | 4.06                        |

Results of a configuration of the buffer project in FPGAs

Fig.7. Data buffer structure derived by the Vivado design tool

## Synthesis framework

As one can see from the method description and the design example, the considered algorithm is given in the graphical form effectively. For the design method investigations, the synthesis framework is developed named SDFCAD [42]. The framework is able to perform the graphical input of SDF of the DSP algorithms with the given period L and data bit width. SDF can be optimized either manually or automatically using one of the genetic programming algorithms [40]. One of two strategies of the buffer design are used by the optimization as well. In particular, the pipelined buffers for the DCT processor are synthesized automatically very well [42].

#### Conclusions

A new method of the data buffer design is proposed, which is intended for the complex pipelined datapaths development and configuring in FPGA. The method is based on the SDF representation in the three-dimensional space, optimization them and describing in VHDL. Depending on the optimization method the derived buffer is based either on RAM or on the register pipeline. The feature of the method consists in that the pipeline buffer is inferred into the SRL16 primitives of the AMD-Xilinx FPGA series which substantially saves the hardware. The method is built in the experimental SDFCAD framework intended for the pipelined datapath synthesis.

#### References

[1] D. Koch, F. Hannig, and D. Ziener, *FPGAs for Software Programmers*. Springer, 2016, p. 327.

[2] Uwe Meyer-Baese, *Digital Signal Processing with Field Programmable Gate Arrays*. Heidelberg: Springer Berlin, 2014, p. 930.

[3] K. Kim and P. Kumar, "Parallel memory systems for image processing," in *Proceedings CVPR* '89: *IEEE Computer Society Conference on Computer Vision and Pattern Recognition*, pp. 654–659. doi: https://doi.org/10.1109/CVPR.1989.37915.

[4] S. Khan, D. Bailey, and G. S. Gupta, "Simulation of Triple Buffer Scheme (Comparison with Double Buffering Scheme)," in *2009 Second International Conference on Computer and Electrical Engineering*, pp. 403–407. doi: https://doi.org/10.1109/ICCEE.2009.226.

[5] S. Churiwala, Designing with Xilinx® FPGAs : Using Vivado. Switzerland: Springer, 2017.

Table1.

[6] Hartmut F.-W. Sadrozinski and J. Wu, *Applications of Field-Programmable Gate Arrays in Scientific Research*. CRC Press and Taylor & Francis, 2011, p. 144.

[7] P. Sedcole, K. Cheung, G. A. Constantinides, and W. Luk, "RunTime Integration of Reconfigurable Video Processing Systems," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 15, no. 9, pp. 1003–1016, doi: https://doi.org/10.1109/TVLSI.2007.902203.

[8] K. Sano and H. Nakahara, "Hardware Algorithms," in *Principles and Structures of FPGAs*, H. Amano, Ed., Springer Singapore, 2018, pp. 137–177. doi: https://doi.org/10.1007/9789811308246\_6.

[9] V. Sklyarov, I. Skliarova, A. Barkalov, and L. Titarenko, *Synthesis and Optimization of FPGA-Based Systems*. Cham Springer International Publishing, 2014, p. 432.

[10] D. G. Bailey, *Design for Embedded Image Processing on FPGAs*. John Wiley & Sons, 2011, p. 482.

[11] R. Sass and A. G. Schmidt, *Embedded Systems Design with Platform FPGAs*. Morgan Kaufmann, 2010, p. 389.

[12] F. Winterstein, K. Fleming, H.-J. Yang, S. Bayliss, and G. Constantinides, "MATCHUP: Memory abstractions for heap manipulating programs," presented at the FPGA '15: Proceedings of the 2015 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, Monterey, California, USA: Association for Computing Machinery, 2015, pp. 136–145. doi: https://doi.org/10.1145/2684746.2689073.

[13] R. Woods, J. McAllister, G. Lightbody, and Y. Yi, *FPGA-based implementation of signal processing systems*, 2nd Ed. Hoboken, Nj : Wiley, 2017, p. 448.

[14] L. Granado and O. Berreteaga, "Creating Rich Human-machine Interfaces with Rational Rhapsody and Qt for Industrial Multi-core Real-time Applications," *Procedia Manufacturing*, vol. 3, pp. 1903–1909, 2015, doi: https://doi.org/10.1016/j.promfg.2015.07.233.

[15] J. Hwang, B. Milne, N. Shirazi, and J. D. Stroomer, "System Level Tools for DSP in FPGAs," in *FieldProgrammable Logic and Applications*, G. Brebner and R. Woods, Eds., Berlin, Heidelberg: Springer Berlin Heidelberg, 2001, pp. 534–543.

[16] K. K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementation. Wiley, 1999, p. 784.

[17] E. A. Lee, S. Neuendorffer, and M. Wirthlin, "Actor-Oriented Design of Embedded Hardware and Software Systems," *Journal of Circuits System and Computers*, vol. 12, no. 03, pp. 231–260, Jun. 2003, doi: https://doi.org/10.1142/s0218126603000751.

[18] M. Ruvald Pedersen and J. Madsen, "Optimal register allocation by augmented leftedge algorithm on arbitrary controlflow structures," in *NORCHIP 2012*, pp. 1–6. doi: https://doi.org/10.1109/NORCHP.2012.6403107.

[19] P. K. Murthy and E. A. Lee, "Multidimensional synchronous dataflow," *IEEE Transactions on Signal Processing*, vol. 50, no. 8, pp. 2064–2079, doi: https://doi.org/10.1109/TSP.2002.800830.

[20] J. Cong, W. Jiang, B. Liu, and Y. Zou, "Automatic memory partitioning and scheduling for throughput and power optimization," presented at the IEEE/ACM International Conference on Computer-Aided Design, San Jose, California: Association for Computing Machinery, 2009, pp. 697–704. doi: https://doi.org/10.1145/1687399.1687528.

[21] Y. Wang, P. Li, and J. Cong, "Theory and algorithm for generalized memory partitioning in high-level synthesis," presented at the FPGA '14: Proceedings of the 2014 ACM/SIGDA International Symposium on Field-programmable Gate arrays., Monterey, California, USA: Association for Computing Machinery, 2014, pp. 199–208. doi: https://doi.org/10.1145/2554688.2554780.

[22] J. Cong and J. Wang, "PolySA: PolyhedralBased Systolic Array AutoCompilation," in 2018 IEEE/ACM International Conference on ComputerAided Design (ICCAD), pp. 1–8. doi: https://doi.org/10.1145/3240765.3240838.

[23] L. Gallo, A. Cilardo, D. Thomas, S. Bayliss, and G. A. Constantinides, "Area implications of memory partitioning for highlevel synthesis on FPGAs," in *2014 24th International Conference on Field Programmable Logic and Applications (FPL)*, pp. 1–4. doi: https://doi.org/10.1109/FPL.2014.6927417.

[24] Y. Wang, P. Zhang, X. Cheng, and J. Cong, "An integrated and automated memory optimization flow for FPGA behavioral synthesis," in *17th Asia and South Pacific Design Automation Conference*, pp. 257–262. doi: https://doi.org/10.1109/ASPDAC.2012.6164955.

[25] Z. Guo, W. Najjar, and B. Buyukkurt, "Efficient hardware code generation for FPGAs," *ACM Trans. Archit. Code Optim.*, vol. 5, Art. no. 1, 2008, doi: https://doi.org/10.1145/1369396.1369402.

[26] R. Shi, J. S. J. Wong, and H. K. H. So, "HighThroughput Line Buffer Microarchitecture for Arbitrary Sized Streaming Image Processing," *Journal of Imaging*, vol. 5, no. 3, 2019, doi: https://doi.org/10.3390/jimaging5030034.

[27] D. G. Bailey and Ambikumar, Anoop S, "Border Handling for 2D Transpose Filter Structures on an FPGA," *Journal of Imaging*, vol. 4, no. 12, 2018, doi: https://doi.org/10.3390/jimaging4120138.

[28] Y. Ikarashi, J. RaganKelley, T. Fukusato, J. Kato, and T. Igarashi, "Guided Optimization for Image Processing Pipelines," in 2021 IEEE Symposium on Visual Languages and HumanCentric Computing (VL/HCC), pp. 1–5. doi: https://doi.org/10.1109/VL/HCC51201.2021.9576341.

[29] M. A. Özkan, O. Reiche, F. Hannig, and J. Teich, "FPGAbased accelerator design from a domainspecific language," in 2016 26th International Conference on Field Programmable Logic and Applications (FPL), pp. 1–9. doi: https://doi.org/10.1109/FPL.2016.7577357.

[30] Z. Guo, W. Najjar, and B. Buyukkurt, "Efficient hardware code generation for FPGAs," *ACM Trans. Archit. Code Optim.*, vol. 5, Art. no. 1, 2008, doi: https://doi.org/10.1145/1369396.1369402.

[31] W. A. Najjar, J. Villarreal, and R. J. Halstead, "ROCCC 2.0," in *FPGAs for Software Programmers*, D. Koch, F. Hannig, and D. Ziener, Eds., Cham: Springer International Publishing, 2016, pp. 191–204. doi: https://doi.org/10.1007/9783319264080\_11.

[32] "UltraFast Design Methodology Guide for the Vivado Design Suite (v2013.3)." Accessed: Oct. 23, 2013. [Online]. Available: www.xilinx.com

[33] "7 Series FPGAs Memory Resources User Guide. UG473 (v1.14)." Accessed: Jul. 03, 2019. [Online]. Available: www.xilinx.com

[34] "Intel® Hyperflex<sup>TM</sup> Architecture High Performance Design Handbook," Oct. 2021. Available: https://www.intel.com/programmable/technical-pdfs/683353.pdf

[35] J. Chu and M. Benaissa, "Low area memoryfree FPGA implementation of the AES algorithm," in *22nd International Conference on Field Programmable Logic and Applications (FPL)*, pp. 623–626. doi: https://doi.org/10.1109/FPL.2012.6339250.

[36] A. Sergiyenko, O. Maslennikow, and Y. Vinogradow, "Tensor approach to the application specific processor design," in 2009 10th International ConferenceThe Experience of Designing and Application of CAD Systems in Microelectronics, pp. 146–149.

[37] A. Sergiyenko, A. Serhienko, and A. Simonenko, "A method for synchronous dataflow retiming," in 2017 IEEE First Ukraine Conference on Electrical and Computer Engineering (UKRCON), pp. 1015–1018. doi: https://doi.org/10.1109/UKRCON.2017.8100404.

[38] A. M. Sergiyenko and V. P. Simonenko, "Method of synchronous dataflow scheduling," *System research and information technologies*, no. 1, pp. 51–62, Mar. 2016, doi: https://doi.org/10.20535/srit.2308-8893.2016.1.06.

[39] A. M. Sergiyenko and V. P. Simonenko, "Otobrazenie perioditsheskich algorithmov w programmiruemye logitsheskie integralnye schemy," *Electronic Modeling*, vol. 29, no. 2, pp. 49–61, 2007.

[40] A. Sergiyenko, A. Serhienko, and V. Romankevich, "Genetic Programming of Pipelined Datapaths for FPGA," in 2020 IEEE 40th International Conference on Electronics and Nanotechnology (ELNANO), pp. 802–806. doi: https://doi.org/10.1109/ELNANO50318.2020.9088773.

[41] A. Sergiyenko, A. Serhienko, and V. Romankevich, "Genetic Programming of Discrete Cosine Transform Processors," presented at the 6-th International Conference on High-Performance Computing (HPC-UA 2020), 2020, pp. 1–6.

# ORGANIZATION OF FAST EXPONENTIATION ON GALOIS FIELDS FOR CRYPTOGRAPHIC DATA PROTECTION SYSTEMS

## Al-Mrayt Ghassan Abdel Jalil Halil, O. Markovskyi, A. Stupak

The article proposes the organization of accelerated execution of the basic operation of a wide range of cryptographic algorithms with a public key-exponentiation on finite Galois fields  $GF(2^n)$ . Acceleration of the computational implementation of this operation is achieved by organizing the processing of several bits of the code at once during squaring on Galois fields. This organization is based on the use of polynomial squared properties, Montgomery group reduction, and extensive use of previous calculations. Procedures for performing basic operations of exponentiation on Galois fields are developed in detail, the work of which is illustrated by numerical examples. It has been proved that the proposed organization can increase the computational speed of this operation by 2.4 times, which is significant for cryptographic applications.

*Key words*: multiplication operation on Galois fields, cryptographic algorithms based on Galois Fields algebra, Galois Fields exponentiation, Montgomery reduction.

#### Introduction

The algebra of finite Galois fields, whose fundamentals were developed in the first half of the 19th century, only gained widespread use in information technology at the beginning of the 21st century. Currently, the mathematical principles of this algebra are the basis for many of the most advanced modern technologies, including mobile communication, high-speed data transmission, mechanisms for restoring lost data, cryptographic data protection, and information security [1]. One of the most significant properties of Galois fields is that regardless of the choice of the generating polynomial, it is feasible to generate a set of algebraic bases whose results will be different [2]. Using this property, it was possible to implement the concept of mathematically distributing communications carried out on the same carrier frequency. The implementation of such a concept in mobile communication systems makes it possible to hold thousands of conversations simultaneously while ensuring their reliable separation. This property is the basis for the application of Galois finite field algebra in modern cryptographic data protection mechanisms. In particular, the algebraic properties of Galois fields are the basis for the implementation of nonlinear transformations in the AES algorithm, which is widely used in practice [3]. A number of protocols for asymmetric encryption, identification, and digital signature with a public key [4], and schemes for cryptographically strong identification of remote users, are based on the Galois field algebra.

It is widely known that the effectiveness of cryptographic data protection mechanisms is determined by the level of security achieved by their use. In addition, it is determined by the speed at which their computation is performed. The last criterion is critical for cryptographic algorithms with a public key, the main computing operation of which is exponentiation performed on huge numbers. When using traditional algebra, this basic operation has the form of modular exponentiation. In Galois field algebra, the result of exponentiation is reduced to the field formed by the fundamental polynomial. The computational complexity of exponentiating *n*-bit numbers is  $O(n^3)$  [5]. This means that with a doubling of the bit depth, the amount of computation increases by a factor of 8. In Galois field algebra, this operation is much faster due to the fact that each bit of numbers is processed independently. In modern conditions, when within the framework of cloud technologies, cybercriminals have remote access to high-powered computer systems, there is an objective need to improve the level of security of cryptographic tools. The only way to enhance protection is to increase the number of bits used. And this dramatically slows down the computational implementation of cryptographic protocols. One of the possible ways out of this situation may be to expand the use of the Galois field algebra and search for ways to speed up the exponentiation of multidigit numbers.

Therefore, the scientific problem of accelerating the computing implementation of the exponentiation operation on Galois fields, which is fundamental to cryptographic applications, is of current relevance to the current stage of development of information and computer technologies.

#### Problem statement and review of methods for its solution

The expansion of the use of Galois field algebra in modern cryptographic information security protocols, as well as the potential for achieving a higher speed of exponentiation compared to traditional algebra, has led to intensive study of the problem of efficient computational implementation of basic operations in this algebra using hardware and software [6].

When using the Galois field algebra, for each number  $A=a_{n-1}\cdot 2^{n-1}+a_{n-2}\cdot 2^{n-2}+\ldots+a_1\cdot 2+a_0$ ,  $\forall j \in \{0, 1, \dots, n-1\}$ :  $a_j \in \{0, 1\}$  can be associated with the polynomial  $A(x)=a_{n-1}\cdot x^{n-1}+a_{n-2}\cdot x^{n-2}+\ldots+a_1\cdot x+a_0$ .

The addition operation on Galois fields is reduced to performing XOR and is further denoted by the symbol ' $\oplus$ '. Reduction, or finding the remainder from the polynomial division A(x) by the Galois field polynomial P(x), is further denoted as A rem P to distinguish the operation of finding the remainder from dividing the number A by the number M in ordinary algebra: A mod M. Multiplication operation on the Galois fields A $\otimes$ B rem P, consists of two operations: polynomial multiplication, denoted by the symbol ' $\otimes$ ', and reduction of the polynomial product with respect to the generating polynomial of the field P. The operation of squaring the number A on the Galois field with the generating polynomial P is denoted as A $\otimes$ A rem P or A|<sup>2</sup> rem P. Accordingly, the operation of exponentiation on Galois fields, that is, the calculation of the remainder of the polynomial division of the result of raising the number A to the power of E by the polynomial P, is denoted as A|<sup>E</sup> rem P.

The existing technologies of exponentiation, both in traditional algebra and on Galois fields, are based on the classical algorithm that provides for the sequential analysis of the bits of the exponent code  $E = \{e_{n-1}, e_{n-2}, ..., e_0\}, \forall j \in \{0, 1, ..., n-1\}; e_i \in \{0, 1\}$ . Each step performs a squaring operation on the Galois field and a multiplication operation on the field, depending on the current value of the exponent bit. As each step uses the results of the previous one, the algorithm cannot be parallelized at the bit level of the exponent code.

Currently, there are two versions of this algorithm, which differ in the direction the bits in the exponent code are analyzed. When exponentiating from the high-order digits of the exponent code, at each of n steps, the current result (which is initially equal to one) is squared and multiplied by A if the current bit of the exponent code is equal to one. Correspondingly, the average time t0 of exponentiation from the most significant bits is equal to  $1.5 \cdot n \cdot t_m$ , where  $t_m$  is the multiplication time on the Galois fields. As a result of exponentiation from the least significant digits of the exponent, partial parallelization of calculations within a single step is possible. This makes it possible to speed up calculations by a factor of 1.5 [7].

It can be concluded from the above discussion that there is no way to accelerate exponentiation on Galois fields at the level of classical algorithms. This means that speeding up the operation of exponentiation on Galois fields can be achieved by reducing the time of performing the most multiplicative operations on Galois fields: multiplication and squaring [8].

Generally, these operations are divided into two phases: polynomial multiplication (polynomial squaring) and reduction, which involves finding the remainder of the polynomial division of the result of the first phase using the forming polynomial P(x) of the Galois field. The operation of polynomial multiplication of *n*-bit numbers requires  $0.5 \cdot n$  logical addition operations and n shift operations and *n* bit value testing operations to calculate the product. Taking into account that the execution time of the logical addition command is approximately the same as the execution time of the shift command, it can be assumed that the implementation of polynomial multiplication is determined by the execution time of  $2.5 \cdot n$  logical operations.

During polynomial reduction, the number corresponding to the generating polynomial is added to the current remainder. This operation includes determining the position of the most significant digit of the current remainder, shifting the code of the forming polynomial, logically adding it to the current remainder. Thus, to perform the reduction, it is necessary to perform an average of n bit test operations,  $2 \cdot n$  shift operations (shifting the code of the generating polynomial and the test code containing one unit), as well as  $0.5 \cdot n$  logical addition operations. In general, the number of logical operations for performing reduction by dividing polynomials is  $3.5 \cdot n$ . Thus, the total number of logical operations required to implement the multiplication of *n*-bit numbers on the Galois fields formed by the polynomial P(x) of degree *n* is  $6 \cdot n$  [8]

The operation of polynomial multiplication is reduced to the logical addition of a maximum of n appropriately shifted multiplicand codes. In theory, the minimum time for this operation is determined by the number of  $\log_2 n$  operations of logical addition. Considering the fact that in real applications the value of n is several thousand, the specified approach to accelerating polynomial multiplication can be applied only within the framework of hardware implementations [9].

Almost all researchers consider the reduction operation as the primary source of acceleration for multiplication on Galois fields. This means that further reduction in the time for multiplication is achieved by speeding up the reduction operation. Most of the known methods [10-13] are based on the use of previous calculation depending on the constant polynomial P(x), which in cryptographic information protection systems is part of the public key and, accordingly, rarely changes.

In acceleration methods based on the use of this property of the generating polynomial, the remainders from the division of codes  $2^{n+1}$ , ...,  $2^{2\cdot n}$  by the generating polynomial P(x) are precalculated:  $P(x) : Q_1 = 2^{n+1}$  rem P,  $Q_2 = 2^{n+2}$  rem P, ...,  $Q_n = 2^{2\cdot n}$  rem P. The calculated codes are stored in the tabular memory of precalculations. The reduction is reduced to the addition of tabular codes that correlate with the units in the higher n digits of the code of the polynomial product. For this, it is necessary to perform an analysis of the higher n digits of the code of the polynomial product, which requires  $2 \cdot n$  logical operations (n operations are required, on the whole, to add the results of recalculations. Thus, due to the use of previous calculations, it is possible to reduce the average number of logical operations for multiplication on Galois fields is  $5 \cdot n$ .

There is another method of speeding up multiplication on Galois fields by combining both phases: polynomial multiplication and reduction using Montgomery technology [14]. In [15], a modification of the Montgomery technology, known in traditional algebra, to the peculiarities of the algebra of Galois fields is proposed. As a result of modifying Montgomery technology for the specifics of Galois fields, the number of logical operations for computing multiplication on Galois fields was reduced to  $4.5 \cdot n$ .

#### Purpose and objectives of research

In the current research, the objective is to accelerate the execution of the exponentiation operation on Galois fields, which is essential to the operation of cryptographic protocols. This will be accomplished through the application of precomputation, which facilitates the simultaneous execution of several operations.

In order to accomplish the set goal, the following scientific problems are solved:

- study of the specific properties of the squaring operation on Galois fields, which allow the execution time of several operations to be combined by using the results of previous calculations;

- development, on the basis of the specified specific properties, of the method of accelerated elevation to the square on Galois fields, which, due to the use of previous calculations, allows to combine the operation of adding a multiple and correcting the intermediate result, as well as to combine the processing of several adjacent digits of the multiplier in time;

– analyzing the performance of the developed organization of fast exponentiation on finite Galois fields and comparing it with other known methods designed to accelerate the calculation of exponents;

- study of the proposed organization of fast exponentiation on Galois fields based on software modeling.

#### Accelerated squaring method on Galois fields with Montgomery group reduction.

The main amount of calculations in exponentiation on Galois fields falls on the operation of squaring. As the main reserves for reducing the number of logical operations when squaring on Galois fields, we can consider:

- use of the property of a polynomial square;

- application of Montgomery reduction modified for Galois fields;

- group processing of discharges when performing the Montgomery reduction.

The basic property of a polynomial square that can be used to speed up calculations is that the polynomial square A $\otimes$ A of a binary number A =  $a_{n-1} \cdot 2^{n-1} + a_{n-2} \cdot 2^{n-2} + \ldots + a_2 \cdot 2^2 + a_1 \cdot 2 + a_0$ ,  $\exists e \{0,1\}$  is equal to the number A $\otimes$ A =  $a_{n-1} \cdot 2^{2 \cdot (n-1)} + a_{n-2} \cdot 2^{2 \cdot (n-2)} + \ldots + a_2 \cdot 2^{2 \cdot 2} + a_1 \cdot 2 + a_0$  [6] This means that polynomial squaring is reduced to inserting zeros between the binary digits of the number A. For example, if A= 14 = 11102, then A $\otimes$ A = 10101002 = 84.

It follows from the above that performing polynomial squaring comes down to shifts in software implementation and permutation of bits in hardware implementation. This means that when using the Montgomery reduction modified for the Galois field, the algorithm for squaring the number A reduces to the following sequence of actions:

- 1. The cycle counter j is set to zero: j=0, as well as the (n+1)-bit result code R: R=0.

- Shift R is performed: R>>=1. If the value of *j* is even, *j* mod 2 =0, then the most significant digit of *r<sub>n</sub>* is filled with the value of the least significant digit *a*<sub>0</sub> of the number A: *r<sub>n</sub>* = *a*<sub>0</sub>. Shift A: A>>=1. If the value of *j* is odd, then the most significant bit of *r<sub>n</sub>* is filled with zero: *r<sub>n</sub>* =0. Increment *j*: *j* = *j*+1. If *j* < *n*, return to repeat step 2. If *j* > 2·*n* go to step 4

- 3. If  $r_0=0$ , then code P is logically added to the current result P:  $R = R \oplus P$ . Return to repeat step 2.

- 4. End of procedure. The value  $R = A \otimes A \otimes U^{-1}$  rem P,  $U^{-1}$  is the multiplicative inversion of the polynomial  $Q(x)=x^n$  on the Galois field formed by the polynomial P(x), i.e.  $U \otimes U^{-1}$  rem P =1.

In order to obtain the correct value of the square of the number A on the Galois field, the result of the procedure should be multiplied by U:  $R' = R \otimes U$  rem P. However, the specified correction is not performed during exposure.

The described procedure of squaring on the Galois field is illustrated by the example of squaring the number  $A = 12_{10} = 1100_2$  on the Galois field, formed by the polynomial  $P(x) = x^4 + x^2 + x + 1$ , which corresponds to the number  $P=10111_2=23_{10}$ ; n = 4, a  $U=10000_2 = 32$ ,  $U^{-1} = 8_{10} = 1000_2$ . Indeed,  $U \cdot U^{-1}$  rem P = 32.8 rem 23 = 1. Real result R'=A $\otimes$ A rem  $P = 12 \otimes 12$  rem 23 = 12. Step-by-step change of variables R and A in the process of performing the above procedure of squaring A = 12 on the Galois field, with a generating polynomial  $P(x) = x^4 + x^2 + x + 1$  is shown in Table 1.

The result R is the product  $A \otimes A \otimes U^{-1}$  rem  $P = 12 \otimes 12 \otimes 8$  rem 23 = 9. To obtain the correct value of the square of the number A=12 on the Galois field, multiply the result R by the value U: R'=R $\otimes$ U rem P = 9 $\otimes$ 16 rem 19 = 12.

The execution of the above procedure involves performing *n* shifts of the number A,  $2 \cdot n$  shifts of the number R, on average  $0.5 \cdot n$  logical addition operations (XOR), *n* bit value testing operations. Thus, the total number of logical operations required to implement the proposed squaring procedure on the Galois field is  $3.5 \cdot n$ .

The main advantage of the proposed procedure is that it eliminates the testing of bits of the multiplier A. This opens up opportunities for group processing of several digits of the number and, thereby, reducing the amount of required calculations.

To theoretically substantiate the possibility of Montgomery group reduction, we prove that for any intermediate result code  $\mathbf{R} = r_n \cdot 2^n + r_{n-1} \cdot 2^{n-1} + \ldots + r_{k-1} \cdot 2^{k-1} + \ldots + r_1 \cdot 2 + r_0$ , where  $\forall j \in \{0, 1, \ldots, n\}$ :  $r_j \in \{0, 1\}$ , there is a linear combination  $\mathbf{L}(\mathbf{P})$  of no more than k shifted codes  $\mathbf{P}$ :  $\mathbf{L}(\mathbf{P}) = v_{k-1} \cdot 2^{k-1} \cdot \mathbf{P} + v_{k-2} \cdot 2^{k-2} \cdot \mathbf{P} + \ldots + v_1 \cdot 2 \cdot \mathbf{P} + v_0 \cdot \mathbf{P}, \forall i \in \{0, 1, \ldots, k-1\}$ :  $v_i \in \{0, 1\}$ , such that their k lower digits are equal to k least significant digits of  $\mathbf{R}$ . The considered linear combination  $\mathbf{L}(\mathbf{P})$  of shifted kcodes  $\mathbf{P}$  corresponding to the generating polynomial  $\mathbf{P}(\mathbf{x})$  of the nth degree of the Galois field can be represented as an (n+k)-bit code  $\mathbf{D}$ :  $\mathbf{L}(\mathbf{P}) = v_{k-1} \cdot 2^{k-1} \cdot \mathbf{P} + v_{k-2} \cdot 2^{k-2} \cdot \mathbf{P} + \ldots + v_1 \cdot 2 \cdot \mathbf{P} + v_0 \cdot \mathbf{P} = \mathbf{D} = d_{n+k-1} \cdot 2^{n+k-1} + d_{n+k-2} \cdot 2^{n+k-2} + \ldots + d_1 \cdot 2 \oplus d_0$

Each *i*-th bit  $d_i$  from among the *k* least significant bits of the code D can be represented as a logical sum of pairwise products of bit components  $v_0, v_1, ..., v_i$  and bit values  $p_0, p_1, ..., p_i$  such that the sum of their indices is equal to *i*:

$$d_i = v_0 \cdot p_i \oplus v_1 \cdot p_{i-1} \oplus \dots \oplus v_i \cdot p_0 = \bigoplus_{j=0}^i v_j \cdot p_{i-j}.$$

(1)

Table 1.

Dynamics of changes in variables R and A when performing the procedure of squaring A=12 on the Galois field formed by the polynomial  $P(x) = x^4 + x + 1$

| j | Transformation <i>R</i>          | Transformation A   |

|---|----------------------------------|--------------------|

| 0 | R=0 R>>1 = 00000                 | A=1100 A>>1 = 0110 |

| 1 | R= 00000 R>>1 = 00000            | A=0110             |

| 2 | R= 00000 R>>1 = 00000            | A=0110 A>>1 = 0011 |

| 3 | R= 00000 R>>1 = 00000            | A=0011             |

| 4 | R= 10000 R>>1 = 01000            | A=0011 A>>1 = 0001 |

| 5 | R=01000 R>>1 = 00100             | A=0001             |

| 6 | R= 10100 R>>1 = 01010            | A=0001 A>>1 = 0000 |

| 7 | R=01010 R>>1 = 00101 R⊕P = 10010 | A=0000             |

| 8 | R= 10010 R>>1 = 01001            |                    |

If we take into account that the generator polynomial P(x) of the Galois field is prime, then  $p_0=1$ .. With this in mind, the expression for the *i* -th digit  $d_i$  of the number D can be represented as:

$$d_i = v_i \oplus \bigoplus_{j=0}^{i-1} v_j \cdot p_{i-1-j}.$$

(2)

In order to prove that for any of the  $2^{k}-1$  possible combinations (except zeros) of values of the k least significant digits of the number R, one can find a linear combination L(P) of codes P shifted by no more than k digits, it is necessary to show that for any code  $r_{k-1}, r_{k-2}, ..., r_1, r_0$  (except zeros) there exists  $v_{k-1}, v_{k-2}, ..., v_1, v_0$ , such that  $\forall i \in \{0, 1, ..., k-1\}$ :  $r_i = d_i$ . This condition is satisfied if there is a solution for the following system of linear equations:

$$\begin{cases} r_0 = v_0 \\ r_1 = v_1 \oplus v_0 \cdot p_1 \\ r_2 = v_2 \oplus v_1 \cdot p_1 \oplus v_0 \cdot p_2 \\ \vdots \\ r_{k-1} = v_{k-1} \oplus v_{k-2} \cdot p_1 \oplus \dots \oplus v_0 \cdot p_{k-1} \end{cases}$$

(3)

An analysis of system (3) shows that it has a unique solution. Indeed, the value of  $v_0$  is easily found from the first equation of systems (3):  $v_0=r_0$ . The second equation, taking into account the found value  $v_0=r_0$ , contains only one unknown component  $v_1$ , the value of which is uniquely found in the form:  $v_1=r_1\oplus r_0\cdot p_1$ . Similarly, the third equation of system (3), taking into account the found values $v_0$ and  $v_1$ , contains only one known value v3, which is uniquely in the form:  $v_3=r_2\oplus p_1\cdot(r_0\oplus r_1)\oplus r_0\cdot p_2$ . Thus, the analysis of system (3) shows that each of its following equations, including into account the previously identified unknowns, contains only one unknown component, which can be uniquely found from this equation. This means that system (3) always has a unique solution, that is, there always exists a linear combination of numbers P shifted by no more than k-1 positions, such that its lower k digits are equal to the lower k digits of an arbitrary number R. By the proved statement, one can perform Montgomery reduction by k digits of the current result simultaneously when squaring on Galois fields. This will significantly speed up the basic operation of exponentiation on Galois fields.

To do this, it is proposed once for a given generating polynomial P(x) of the Galois field for each of the possible  $2^{k}-1$  (except for zeros) combinations of the *k*-bit code  $r_{k-1}, r_{k-2}, ..., r_1, r_0$  to calculate the values of the sums  $L(P) = v_{k-1} \cdot 2^{k-1} \cdot P + v_{k-2} \cdot 2^{k-2} \cdot P + ... + v_1 \cdot 2 \cdot P + v_0 \cdot P$ , in which the values of *k* least significant digits are equal to the above combination. For given values of  $r_{k-1}, ..., r_0$ , the corresponding values  $v_{k-1}, v_{k-2}, ..., v_1, v_0$  are found as a result of solving the system of equations (3). The calculation results are presented in the form of  $2^{k}-1$  tabular values T(1), T(2), ..., T(2^{k}-1).

The value of *k* is chosen to be even and such that *n* is evenly divisible by it.

The foregoing is illustrated by the following example. Let n=8 and the Galois field is formed by the polynomial  $P(x)=x^8+x^4+x^3+x^2+1$  For n=8, the number U =2<sup>n</sup> =256, and its multiplicative inversion U<sup>-1</sup> with the above generating polynomial P(x) is equal to U<sup>-1</sup>=127; indeed 256 $\otimes$ 127 rem P(x) =1.

This polynomial corresponds to the number  $P=100011101_2 = 285_{10}$ . The lower four digits (for k=4) of this number are:  $p_0=1$ ,  $p_1=0$ ,  $p_2=1 \text{ m } p_3=1$  and  $p_3=1$ . In order to determine the values of  $v_0$ ,  $v_1$ ,  $v_2$  and  $v_3$  at which the lower three digits of the linear combination  $v_3 \cdot 2^3 \cdot P \oplus v_2 \cdot 2^2 \cdot P \oplus v_1 \cdot 2 \cdot P \oplus v_0 \cdot P$  are equal to 1010, i.e.  $r_3=1$ ,  $r_2=0$ ,  $r_1=1$ ,  $r_0=0$  it is necessary to solve the system of equations (4) which, in the framework of the example, has the following form:

$$\begin{cases}

0 = v_0 \\

1 = v_1 \\

0 = v_2 \oplus v_0 \\

1 = v_3 \oplus v_1 \oplus v_0

\end{cases}$$

(4)

Substituting the found value  $v_0=0$  into the third equation, it is easy to determine  $v_2=0$ . Similarly,  $v_3=0$  is deduced from the fourth equation. The found values determine the linear combination:  $4 \cdot P \oplus P = 2 \cdot 285 = 570_{10} = 0010 \ 0011 \ 1010_2$ . Thus, the table value T[1010] = T[10] = 570. The four least significant bits of this linear combination are equal to 1010. Similarly, linear combinations can be constructed for all possible 4-bit codes from 0001 to 1111, the values of which are summarized in Table 2.

In addition, to quickly form *k*-bit fragments of a polynomial square from k/2-bit fragments of a number by inserting zeros between their bits, it is proposed to create and use a Z table. Such a table contains polynomial squares obtained by inserting zeros for each of  $2^{k/2}-1$  k/2-bit codes. In particular, k=4 table Z consists of three rows:  $Z[1] = Z[01_2] = 0001_2$ ,  $Z[10_2] = 0100_2$  and  $Z[11_2] = 0101$ .

The actions outlined above, depending only on the generating polynomial P(x) and the number k of simultaneously processed bits, are carried out only once for cryptographic data protection systems, since the polynomial is part of the public key.

Calculation of the square  $A \otimes A$  rem P of the number A on the Galois field is proposed to be performed in the following sequence:

1. The cycle counter j is set to zero: j=1, as well as the (n+k)-bit result code R: R=0.

2. R is shifted by *k* bits: R>>=k. The upper k digits of R are filled with a table code, the number of which is determined by the lower k/2 digits of A:  $Z(a_{k/2-1}, a_{k/2-2}, ..., a_1, a_0)$ .

3. If the lower k bits of R:  $r_{k-1}, r_{k-2}, ..., r_0$  are equal to zero, go to step 4. Otherwise, the code  $T[r_{k-1}, r_{k-2}, ..., r_0]$  is logically added to R:  $R = R \oplus T[r_{k-1}, r_{k-2}, ..., r_0]$ .

4. A is shifted by k/2 bits: A>>=k/2.. Increment j: j=j+1. If  $j \le 2 \cdot n/k$ , return to repeat step 2.

The following example illustrates the proposed procedure for accelerated squaring on Galois fields. Let it be necessary to square the number  $A=172_{10} = 1010 \ 1100_2$  on the Galois field with the generating polynomial  $P(x)=x^8+x^6+x^4+x^3$  for which table 2 is constructed for k=4. The true value of the result A $\otimes$ A rem P = 172  $\otimes$  172 rem 285 = 11111\_2=31.

The dynamics of changes in R and A over steps j of the described procedure for accelerated squaring on Galois fields is shown in Table 3.

The result R=66 differs from the true one and is the product  $A \otimes A \otimes U^{-1}$  rem  $P = 172 \otimes 172 \otimes 147$  rem 285. To obtain the real square R' of the number A=172 on the Galois field, it is necessary to perform the Montgomery correction, that is, multiply the result R by the value U: R'=R $\otimes$ U rem P =  $66 \otimes 256$  rem 285 = 31.

Table 2.

Tabular values of the results of precomputations for the Galois field with generating polynomial  $P(x)=x^8+x^4+x^3+x^2+1$  for k=4

| <i>r</i> <sub>3</sub> , <i>r</i> <sub>2</sub> , <i>r</i> <sub>1</sub> , <i>r</i> <sub>0</sub> | Т                                  | <i>r</i> <sub>3</sub> , <i>r</i> <sub>2</sub> , <i>r</i> <sub>1</sub> , <i>r</i> <sub>0</sub> | Т                                  |

|-----------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------|

|                                                                                               |                                    | 1 0 0 0 (8)                                                                                   | $2280_{10} = 1000\ 1110\ 1000_2$   |

| 0001(1)                                                                                       | $1425_{10} = 0101 \ 1001 \ 0001_2$ | 1 0 0 1 (9)                                                                                   | $1385_{10} = 0101\ 0110\ 1001_2$   |

| 0 0 1 0 (2)                                                                                   | $2850_{10} = 1011\ 0010\ 0010_2$   | 1 0 1 0 (10)                                                                                  | $570_{10} = 0010\ 0011\ 1010_2$    |

| 0 0 1 1 (3)                                                                                   | $1875_{10} = 0111 \ 0101 \ 0011_2$ | 1011(11)                                                                                      | $4027_{10} = 1111\ 1011\ 1011_2$   |

| 0 1 0 0 (4)                                                                                   | $1140_{10} = 0100\ 0111\ 0100_2$   | 1 1 0 0 (12)                                                                                  | $3228_{10} = 1100\ 1001\ 1100_2$   |

| 0 1 0 1 (5)                                                                                   | $2565_{10} = 1111\ 0011\ 0101_2$   | 1 1 0 1 (13)                                                                                  | $285_{10} = 0001\ 0001\ 1101_2$    |

| 0 1 1 0 (6)                                                                                   | $3990_{10} = 1111\ 1001\ 0110_2$   | 1 1 1 0 (14)                                                                                  | $1710_{10} = 0110 \ 1010 \ 1110_2$ |

| 0 1 1 1 (7)                                                                                   | $855_{10} = 0011 \ 0101 \ 0111_2$  | 1 1 1 1 (15)                                                                                  | $3135_{10} = 1100\ 0011\ 1111_2$   |

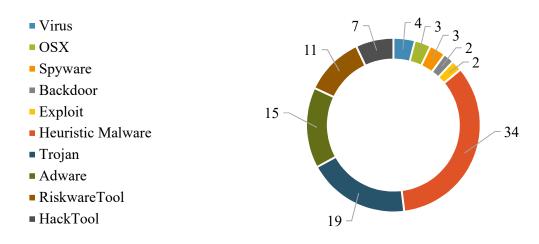

# Table 3